#### UNIVERSITÀ DEGLI STUDI DI BERGAMO School of Engineering

#### Department of ENGINEERING AND APPLIED SCIENCES

# Intelligent systems for particle detectors in environmental applications and High-Energy Physics

Doctoral Dissertation of: Benedetta NODARI

Advisor: Prof. Valerio RE

Co-Advisor: Prof. Aurore SAVOY-NAVARRO

December 2016

# Contents

| C            | onter | nts                                        | <b>2</b> |

|--------------|-------|--------------------------------------------|----------|

| Li           | st of | Figures                                    | 4        |

| $\mathbf{A}$ | bstra | ct                                         | 2        |

| 1            | Intr  | oduction to particle detectors             | 5        |

|              | 1.1   | Motivation                                 | 5        |

|              | 1.2   | Main challenges                            | 9        |

|              | 1.3   | The operating principle                    | 10       |

| 2            | Por   | table Radon detection system               | 12       |

|              | 2.1   | Introduction                               | 12       |

|              | 2.2   | Motivation and Outlines                    | 13       |

|              | 2.3   | Origins of Radon                           | 14       |

|              | 2.4   | Measurement techniques for Radon detection | 15       |

|              | 2.5   | System requirements and goals              | 18       |

|              | 2.6   | Detector and Front-End design              | 21       |

|              |       | 2.6.1 Detector model                       | 28       |

|              |       | 2.6.2 Ventilation system design            | 32       |

|              |       | 2.6.3 Electronics readout design           | 34       |

|              |       | 2.6.4 Noise analysis                       | 42       |

| Bi | bliog | raphy  |                                                    | 124  |

|----|-------|--------|----------------------------------------------------|------|

| Co | onclu | sions  |                                                    | 123  |

|    | 3.9   | Conclu | isions                                             | 120  |

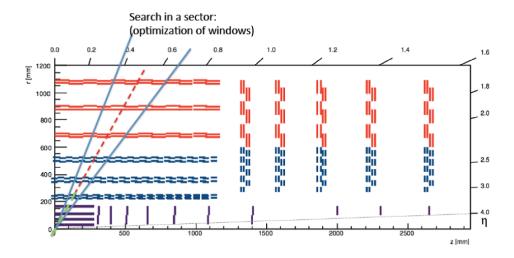

|    |       | 3.8.2  | New ideas for including the Pixels in L1-trigger   |      |

|    |       | 3.8.1  | Level-1 pixel trigger study for CMS                | 112  |

|    | 3.8   | New ic | leas for intelligent digital readout architecture  | 112  |

|    | 3.7   | Prelim | inary ASIC test results                            | 107  |

|    |       | 3.6.4  | New version of pixel layout for RD53A              | 106  |

|    |       | 3.6.3  | Digital design for data readout                    | 103  |

|    |       | 3.6.2  | Simulations                                        | 98   |

|    |       | 3.6.1  | Pixel layout                                       | 96   |

|    | 3.6   | IFCP6  | 5 layout and post-layout simulations               | 96   |

|    |       | 3.5.4  | Simulation performance metrics                     | 94   |

|    |       | 3.5.3  | Comparator                                         | . 88 |

|    |       | 3.5.2  | Small signal analysis                              |      |

|    |       | 3.5.1  | Charge sensitive amplifier                         |      |

|    | 3.5   | Analog | g Front-End design and performances                |      |

|    |       | 3.4.2  | Analog Front-End implementation                    |      |

|    |       | 3.4.1  | Motivation and Basics                              |      |

|    | 3.4   | The sy | vnchronous ADC concept                             |      |

|    |       | 3.3.3  | Power consumption                                  |      |

|    |       | 3.3.2  | Noise                                              |      |

|    | 0.0   | 3.3.1  | Radiation tolerance                                |      |

|    | 3.3   |        | requirements                                       |      |

|    |       | 3.2.3  | The CMS pixel detector                             |      |

|    |       | 3.2.1  | CMS: The particle detector                         |      |

|    | 3.2   | 3.2.1  | The Large Hadron Collider (LHC)                    |      |

|    | 3.2   |        | ation and Outlines                                 |      |

| 3  | 3.1   | _      | Analog Front-End for future pixel detectors uction |      |

| 3  | Dog   | ion of | Analag Front End for future nivel detectors        | 56   |

|    | 2.9   | Conclu | ısion                                              | 55   |

|    | 2.8   | System | n measurements                                     | 49   |

|    | 2.7   | Printe | d Circuit Board design                             | 43   |

|    |       |        |                                                    |      |

# List of Figures

| Common electromagnetic spectrum                                        | O                   |

|------------------------------------------------------------------------|---------------------|

| Uranium decay chain                                                    | 14                  |

| Radon geology in Italy (a) and in the USA (b) $\dots$                  | 16                  |

| Signal-to-noise ratio for different flows at a 0.4 pCi/l activity $$ . | 21                  |

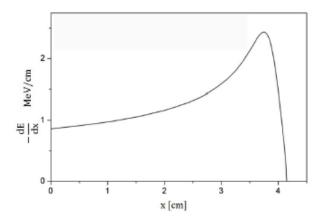

| Typical Bragg curve for 5.49 MeV alpha particles in air                | 22                  |

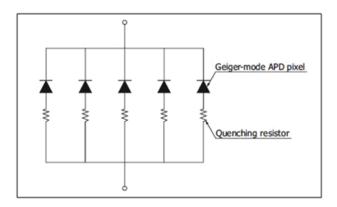

| Simplified schema of a silicon photomultiplier                         | 24                  |

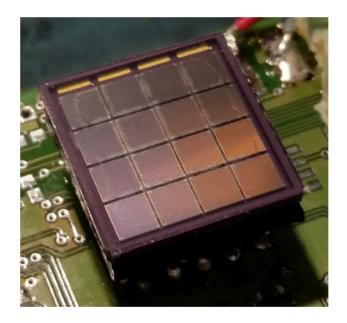

| SensL Array SB-4, silicon photomultiplier                              | 25                  |

| ZnS(Ag)/PhotoMultiplier setup to measure the actual light              |                     |

| output of the scintillator (in photons/MeV)                            | 28                  |

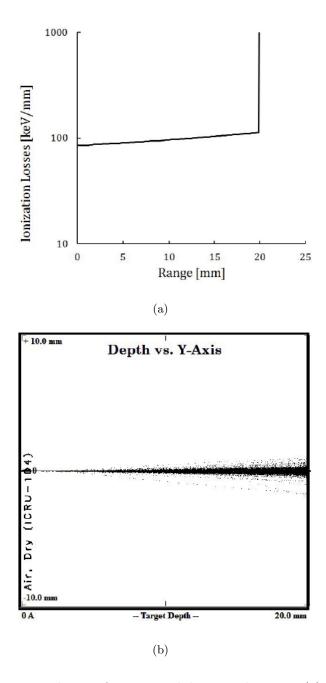

| Ionization losses of 5.6 MeV alpha particles in air (a). An            |                     |

| absorber is put at a 20 mm distance. Alpha tracks in the same          |                     |

| volume of air (b)                                                      | 29                  |

| Alpha particle ionization losses in the detector after transit in      |                     |

| the air volume (a). Tracks within the detector (b)                     | 31                  |

| 3D model section of the tubing system (a). Tubing system               |                     |

| developed by 3D printer (b)                                            | 33                  |

| CFD analysis for piping ventilation system related to velocity         |                     |

| (a) and drop pressure outline (b)                                      | 35                  |

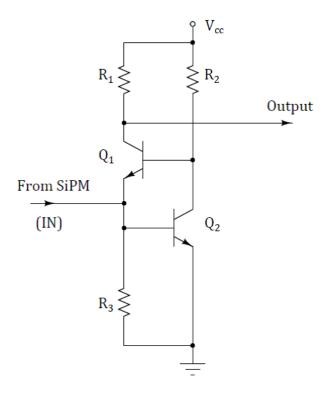

| First stage of the SiPM readout channel                                | 36                  |

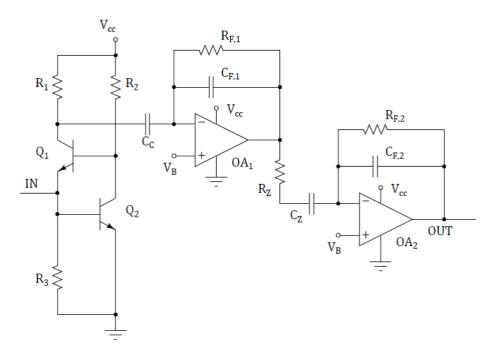

| Preamplifier, first stage and second stage of readout                  | 39                  |

|                                                                        | Uranium decay chain |

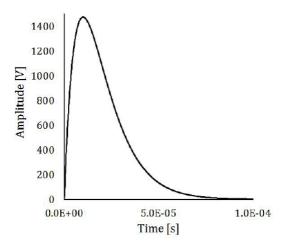

| 2.14 | Calculated filter time response to a unity voltage step for a      |    |

|------|--------------------------------------------------------------------|----|

|      | peaking time of 10 $\mu$ s                                         | 40 |

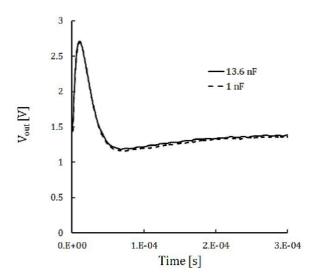

| 2.15 | Comparison between the measured response with a 1 nF and           |    |

|      | 13.6 nF detector capacitance                                       | 41 |

| 2.16 | Equivalent noise circuit for the preamplifier in Figure 2.12. $$   | 42 |

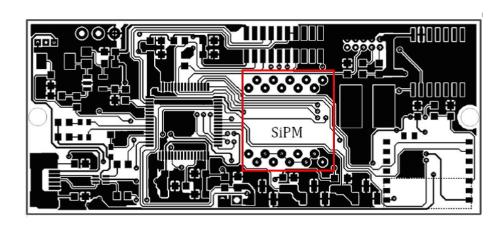

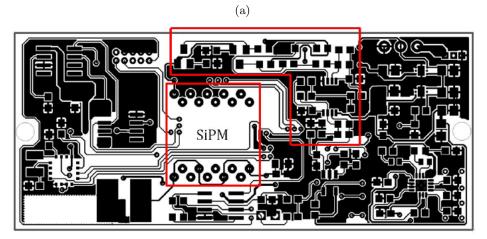

| 2.17 | Prototype board with top (a) and bottom (b) layer                  | 44 |

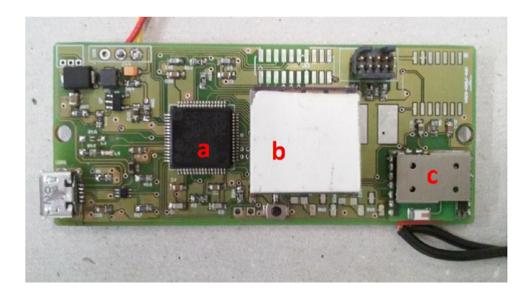

| 2.18 | Picture of the fully assembled board. The microcontroller (a),     |    |

|      | SiPM coupled with a ZnS screen (b) and Bluetooth module are        |    |

|      | shown. The front-end electronics are located on the bottom layer.  | 45 |

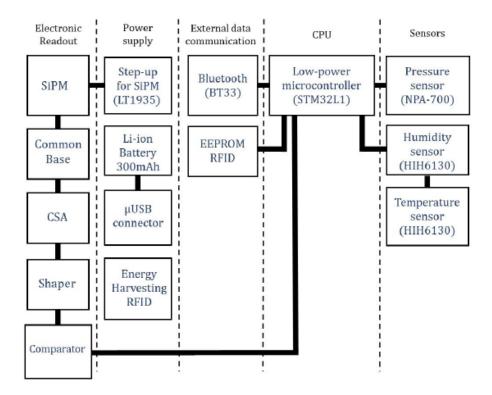

| 2.19 | System block diagram                                               | 46 |

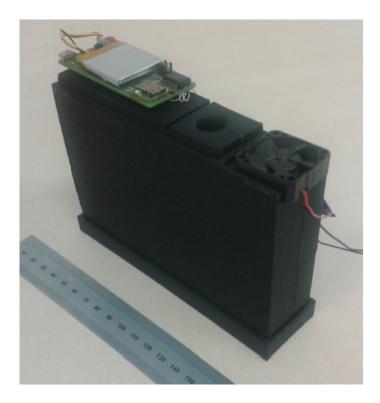

| 2.20 | Fully assembled system                                             | 50 |

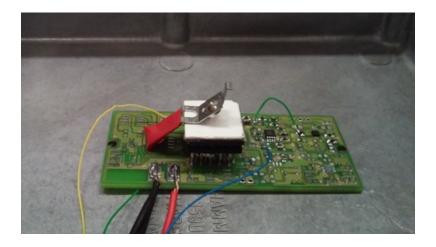

| 2.21 | Preliminary measurement setup                                      | 51 |

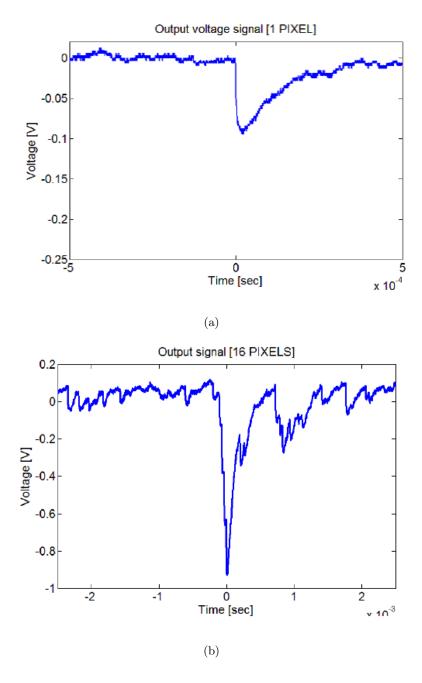

| 2.22 | Output voltage signal with 1 pixel (a) and 16 pixels (b) connected |    |

|      | to the analog front-end                                            | 52 |

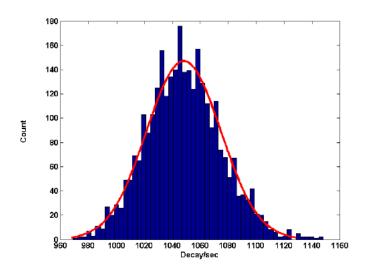

| 2.23 | Histogram of the event rate                                        | 53 |

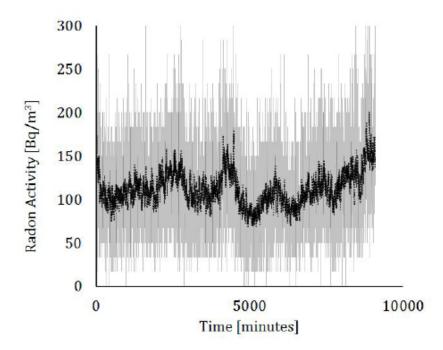

| 2.24 | Acquired radon activity data before (black line) and after (gray   |    |

|      | line) smoothing.                                                   | 53 |

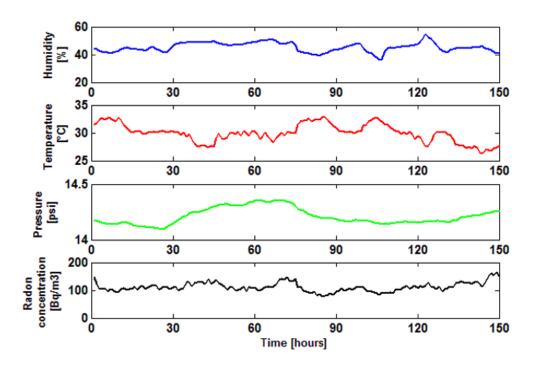

| 2.25 | Smoothed radon activity data and environmental data                | 54 |

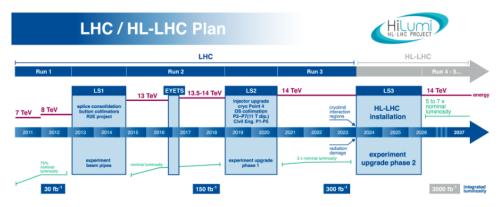

| 3.1  | LHC timeline                                                       | 59 |

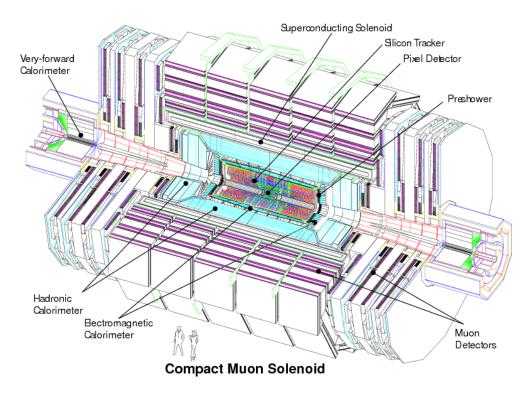

| 3.2  | An exploded view of the CMS detector                               | 60 |

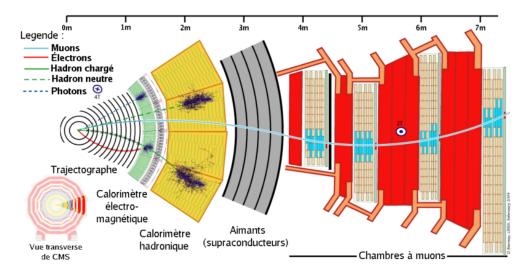

| 3.3  | Transverse section of the CMS detector                             | 61 |

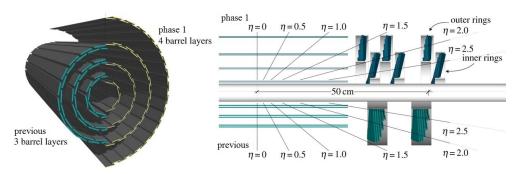

| 3.4  | Barrel geometry of Phase-1 upgrade pixel detector compared to      |    |

|      | the previous phase                                                 | 63 |

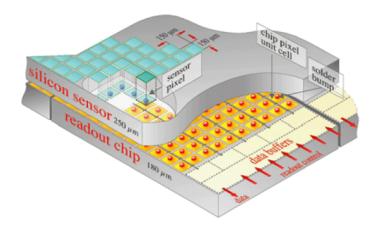

| 3.5  | CMS silicon pixel detector                                         | 63 |

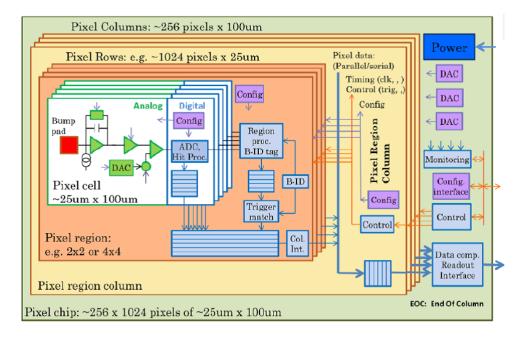

| 3.6  | Block diagram of pixel chip for the inner layer of the CMS silicon |    |

|      | tracker                                                            | 66 |

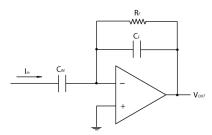

| 3.7  | Block diagram of a common charge signal preamplifier (CSA)         | 73 |

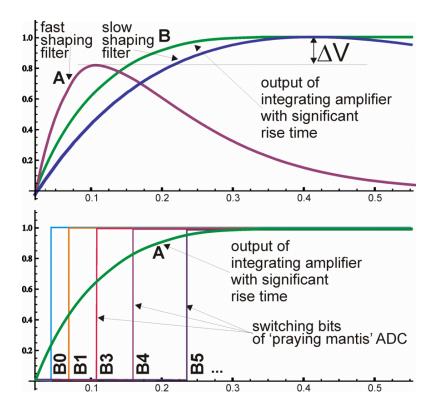

| 3.8  | Trade-off of fast and slow shaping (a). Synchronous ADC concept    |    |

|      | (b)                                                                | 75 |

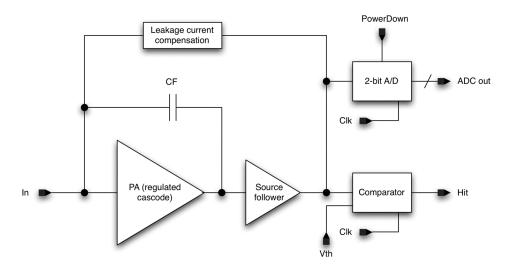

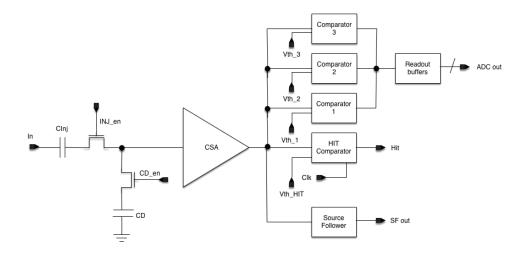

| 3.9  | Block diagram of the analog front-end containing a preamplifier    |    |

|      | with leakage current compensation, an AC-coupled synchronous       |    |

|      | comparator and 3-bit flash ADC                                     | 78 |

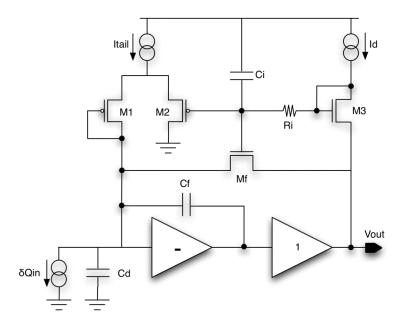

| 3.10 | Simplify schematic of the IFCP65 charge sensitive amplifier,       |    |

|      | featuring a leakage current compensation network                   | 80 |

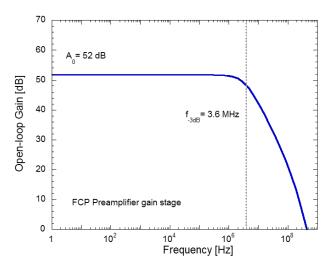

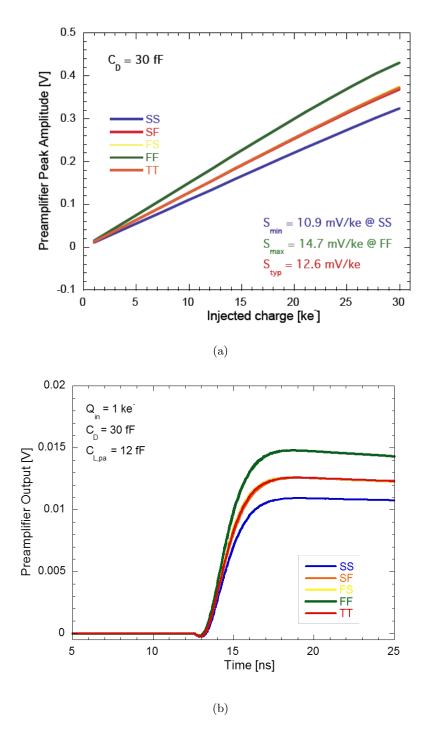

| 3.11 | DC open loop gain                                                     | 81  |

|------|-----------------------------------------------------------------------|-----|

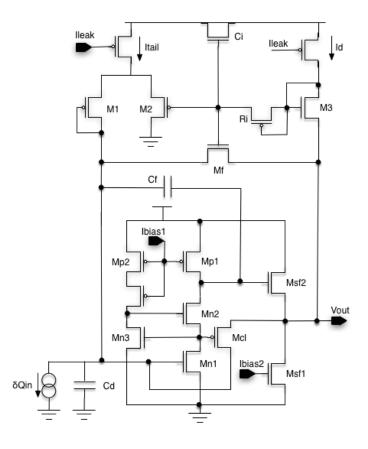

| 3.12 | Transistor level preamplifier design showing a regulated cascode      |     |

|      | core amplifier                                                        | 82  |

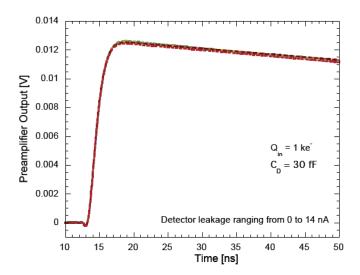

| 3.13 | CSA response to an input charge equal to 1000 electrons, for          |     |

|      | different values of the detector leakage current, ranging from $0$    |     |

|      | to 14 nA                                                              | 84  |

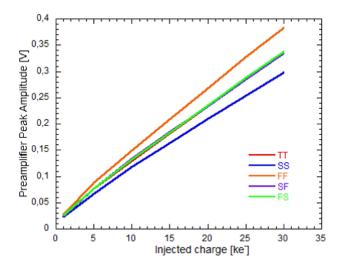

| 3.14 | Four corners simulation of the CSA peak amplitude as a function       |     |

|      | of the input charge (a) and of CSA response to an input charge        |     |

|      | equal to 1000 electrons                                               | 85  |

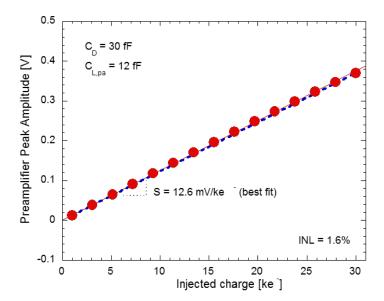

| 3.15 | CSA peak amplitude as a function of the input charge in TT            |     |

|      | corner                                                                | 86  |

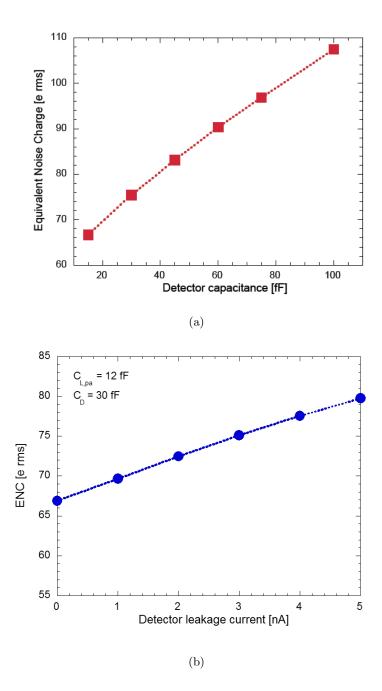

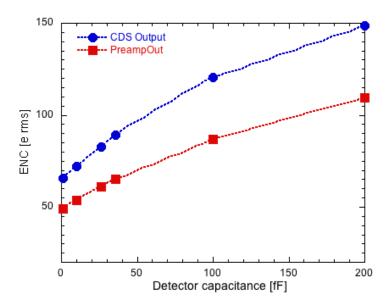

| 3.16 | Equivalent noise charge as a function of the detector capacitance     |     |

|      | $C_D$ (a) and as a function of leakage current (b)                    | 87  |

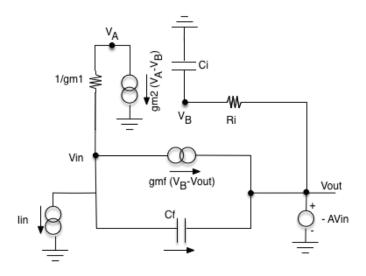

| 3.17 | Small-signal equivalent circuit of the charge sensitive preamplifier. | 88  |

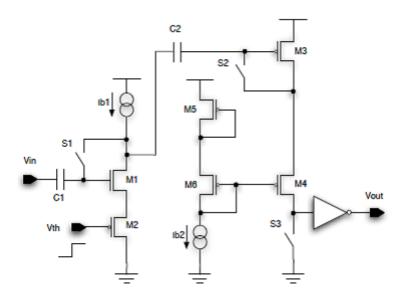

| 3.18 | Simplify schematic of the IFCP65 comparator, based on two             |     |

|      | stages                                                                | 89  |

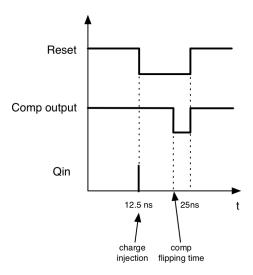

| 3.19 | Simulation timing scheme. Charge injection takes place as soon        |     |

|      | as the reset is released                                              | 90  |

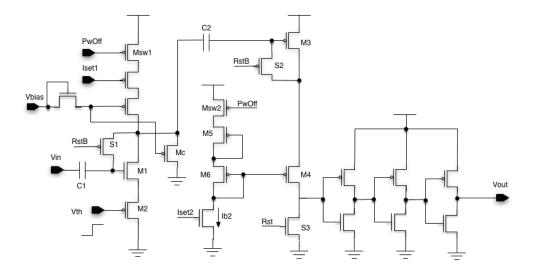

| 3.20 | Transistor level schematic of the IFCP65 comparator                   | 91  |

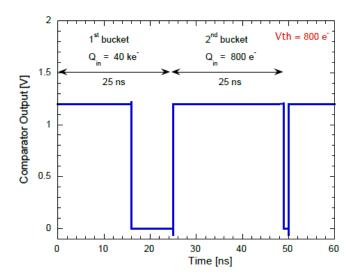

| 3.21 | Comparator output response to two consecutive event, with a           |     |

|      | threshold set to 800 electrons                                        | 93  |

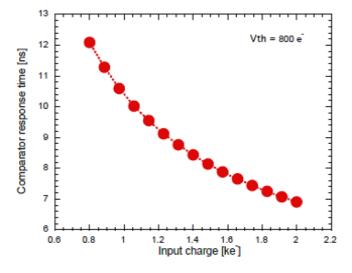

| 3.22 | Comparator response time as a function of the injected charge.        |     |

|      | The threshold is equal to 800 electrons                               | 93  |

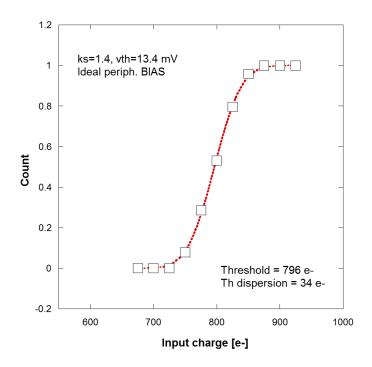

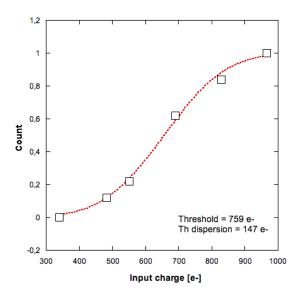

| 3.23 | Threshold dispersion analysis                                         | 95  |

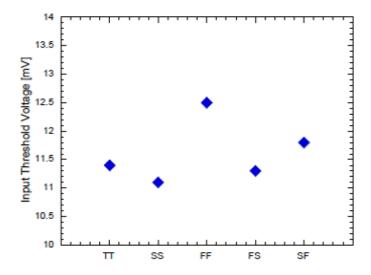

| 3.24 | Amplitude of the threshold voltage step to be provided at the         |     |

|      | comparator input equivalent to a 800 electrons threshold, for         |     |

|      | different simulation corners                                          | 95  |

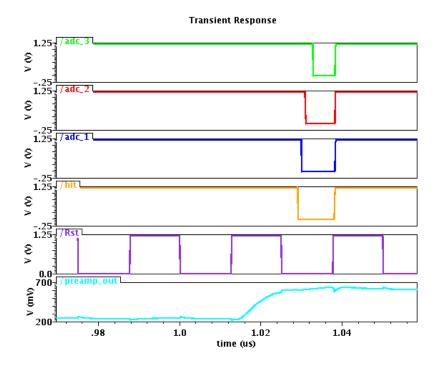

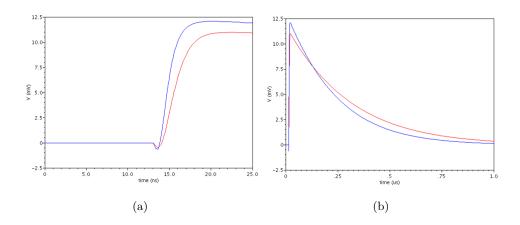

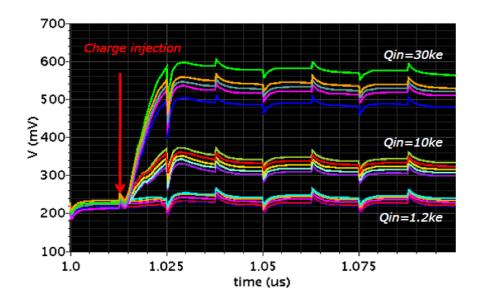

| 3.25 | Simulation of the analog front-end with charge injected at 12.5 ns.   | 96  |

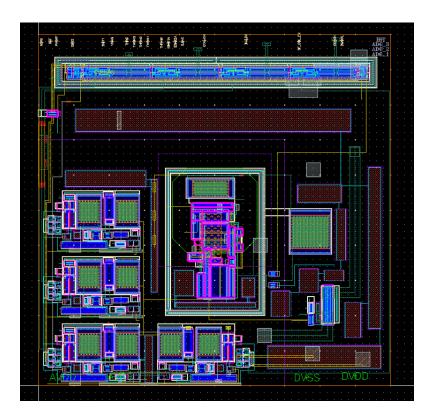

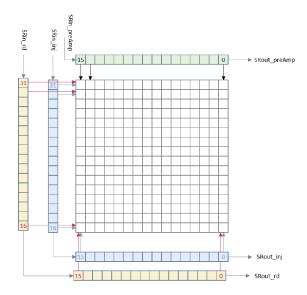

|      | Block diagram of the whole pixel                                      | 98  |

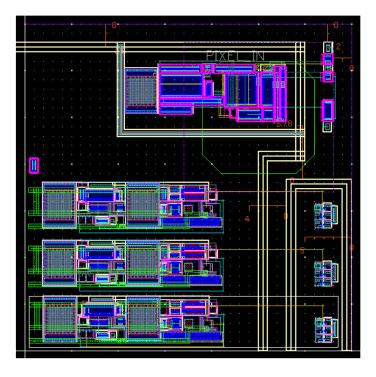

|      | Layout level of the pixel readout front-end                           | 98  |

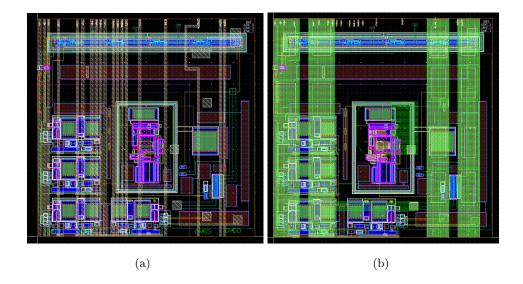

|      | Preamplifier and comparator biasing (a) and power supply and          |     |

|      | ground (b)                                                            | 99  |

| 3.29 | Transient analysis at preamplifier output pre-layout (blu line)       |     |

|      |                                                                       | 100 |

| 3.30 |                                                                       | 100 |

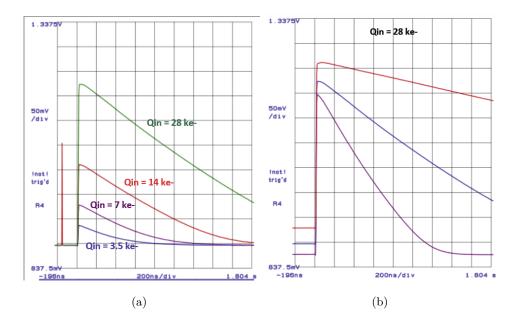

| 3.31 | Post-layout four corner simulations of the CSA peak amplitude       |

|------|---------------------------------------------------------------------|

|      | as a function of the input charge                                   |

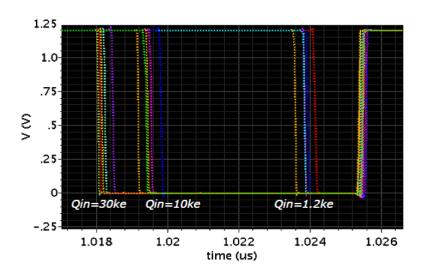

| 3.32 | Post-layout four corner simulations of the comparator output        |

|      | with different input charge                                         |

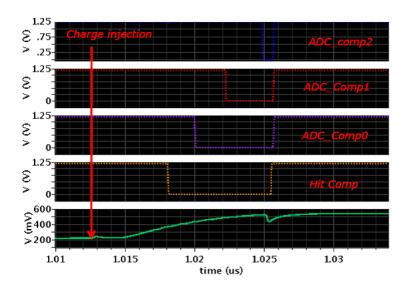

| 3.33 | Hit comparator and ADC comparator outputs in post-layout            |

|      | simulations                                                         |

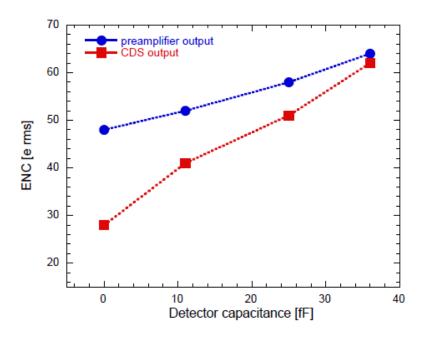

| 3.34 | Simulation of Equivalent Noise Charge as a function of CD           |

|      | including CDS effects                                               |

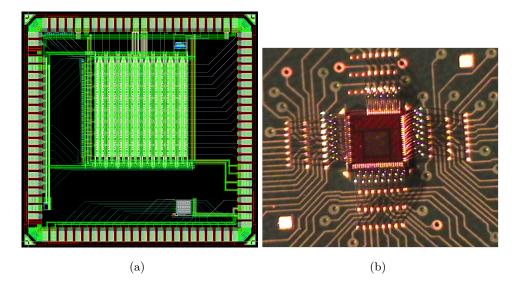

| 3.35 | Layout of the submitted chip (a) Physical bump-bonded chip (b).104  |

| 3.36 | Shift register readout of the pixel matrix                          |

| 3.37 | New version of pixel layout for RD53A project 108                   |

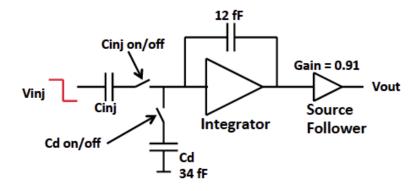

| 3.38 | Integrator time response                                            |

| 3.39 | CSA block diagram                                                   |

| 3.40 | CSA return to baseline for different input charges (a) CSA          |

|      | response for different values of detector leakage current (b) $110$ |

| 3.41 | Equivalent Noise Charge as a function of CD including CDS           |

|      | effects                                                             |

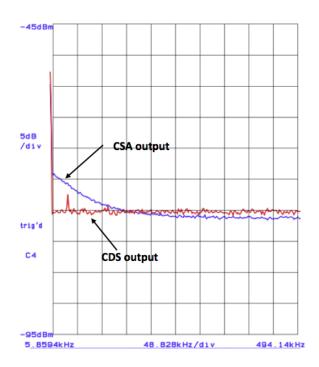

| 3.42 | Low frequency noise spectrum                                        |

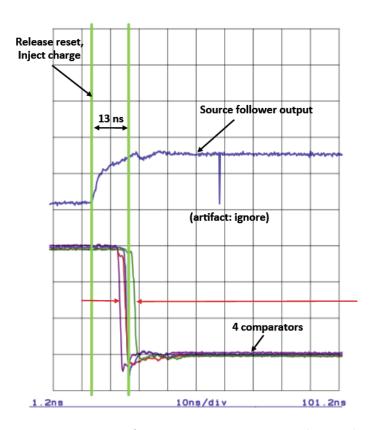

| 3.43 | Test of 4 comparators output in the pixel                           |

| 3.44 | S-curve of Monte Carlo analysis for threshold dispersion 113 $$     |

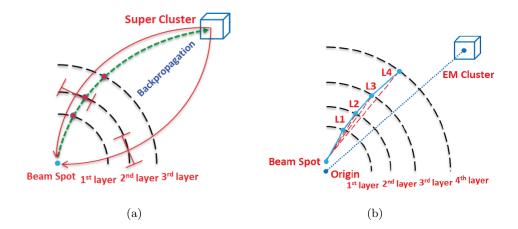

| 3.45 | Matching of the track as defined by the L1 outer tracker trigger    |

|      | with the pixel track segment                                        |

| 3.46 | Schema describing the Pixel matching with the em-cluster. $$ $$ 116 |

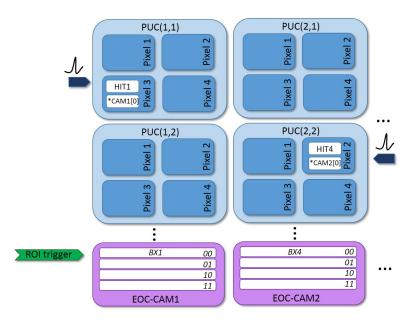

| 3.47 | Schema of the proposed readout architecture including EOC           |

|      | CAMs                                                                |

### **Abstract**

Over the last decades, improvements in microelectronics technology have fostered significant progress in all fields of engineering, science and also in radiation detection. The main challenge in designing radiation detectors is to develop systems based on front-end electronics that is able to cope with high radioactive environment, satisfy very high resolution requirements and comply with high particle rates. This thesis work focuses on the analysis and development of novel and intelligent solutions for electronics system, especially suited for radiation detectors. In particular, two different applications are considered here.

The first one concerns the design of a portable and affordable detector system for continuous indoor Radon detection, based on SiPM technology. A simple analog front-end with optimized low-noise performances and reduced power consumption has been designed for counting each alpha particle that occurs in the detector after Radon decay. The readout electronics is integrated with a suite of environmental sensors on a full-custom Printed Circuit Board. Compared to all the commercial Radon detector nowadays available, the developed system is able to detect reliable value of indoor Radon concentration within few hours. The system also exploits the recent capabilities of microelectronic devices by including advanced functions such as Bluetooth data transmission and energy harvesting.

In high-energy physics experiments, with particular emphasis on the HL-

LHC environment, pixel detectors have to satisfy aggressive requirements concerning high granularity, high rate capability and low power consumption. With the advent of accessible modern technology such as 65 nm CMOS, the processing speed and reduced power consumption can be achieved. In order to meet such specifications, a new pixel mixed signal ASIC has been designed as a prototype front-end for the HL-HLC pixel readout system, within the framework of RD53 collaboration. The ASIC front-end includes signal processing and synchronous analog-to-digital conversion within one Bunch Crossing period. Thus, the emphasis of the work is on the feasibility of a synchronous ADC within the HL-LHC environment, able to ensure high performances in terms of low noise, power dissipation and high speed. Finally, a novel and intelligent digital architecture has been proposed, in order to focus the efforts of the front-end on the implementations of three main features: a novel data sparsification method, a clusterization scheme at the hardware level itself and fast Region-Of-Interest (ROI) trigger capability.

The manuscript is organized in three chapters. The first one introduces the motivations and main challenges related to radiation detectors in various applications, such as high energy physics experiments, medical digital imaging and space science. Then, the second chapter describes the system developed for indoor Radon detection. In particular, it discusses the motivations that lead to such design, along with an overview on Radon origins and common measurements techniques. It also presents the system requirements and goals before explaining the front-end and Printed Circuit Board design. In addition, preliminary measurements are provided in order to demonstrate the feasibility of the developed intelligent system. The last chapter is devoted to the design and preliminary characterization of pixel front-end Application Specific Integrated Circuit, developed as a prototype front-end for the innermost layer of CMS detector and submitted in June 2016. The first section of this chapter provides an overview on HL-LHC environment, along with details on system requirements. Then, it describes a conceptual operating principle of the synchronous ADC and its advantages and implementation technology. Finally, a detailed explanation over the transistor level and layout design of the front-end is provided along with preliminary test results.

# Acknowledgments

First of all, I gratefully acknowledge my advisor Prof. Valerio Re for believing in me since the beginning of my PhD work, for his guidance, supervision and support during these three years.

I would like to thank Prof. Aurore Savoy-Navarro for her helpful support. She gave me the opportunity to work in a very interesting and stimulating scientific environment.

I owe special thanks to Lorenzo Fabris at Oak Ridge Laboratory (Tennessee, USA) for his fundamental contribution in designing the analog front-end section of the Radon detector, as well as in performing most of the simulations related to the detector. In particular, my gratitude to him goes for all the knowledge he shared with me, and also for his support and valuable technical assistance.

To Luigi Gaioni at University of Bergamo goes my deepest gratitude for the immense knowledge he shared with me about the Integrated Circuit design, as well as for his continuous support, his kind availability, for his patience and encouragement.

I want to thank my colleagues from microelectronics laboratory of University of Bergamo, for their support. In particular to Prof. Gianluca Traversi, Prof. Massimo Manghisoni, Michele Caldara, Francesco De Canio, Daniele Comotti, Michael Galizzi, Patrick Locatelli and Elisa Riceputi.

Special thanks for the great and funny time I spent with them during these last months to Alvin Sashala Naik (Merci!), Leônidas Fernandes do Prado

(Obrigada!), Sergei Lapin and Anton Bogachev (спасибо!) and Chenfan Zhang (Xie Xie!), my colleagues from Astroparticule et Cosmologie laboratory (APC) at University Paris Diderot.

Last but not the least, I would like to thank my parents, my two sisters Miriam and Valeria and all my friends, near and far, for cheering and support me during all these years.

The research leading to these results has received funding from the People Programme (Marie Curie Actions) of the European Union's Seventh Framework Programme FP7/2007-2013/ under REA grant agreement n [317446] INFIERI "INtelligent Fast Interconnected and Efficient Devices for Frontier Exploitation in Research and Industry".

## CHAPTER 1

## Introduction to particle detectors

#### 1.1 Motivation

In general, a particle detector, also known as a radiation detector, is defined as a device designed for the detection, tracking and/or identification of ionizing particles, in a multitude of environments and applications. Such subatomic particles are those emitted by radioactive materials, produced by particle accelerators or observed in cosmic rays. They include: electrons, protons, neutrons, alpha and beta particles, gamma rays, and numerous mesons and baryons. In experimental and applied particle physics, nuclear physics, and nuclear engineering, detectors can measure the particle energy and other properties such as momentum, spin, charge, in addition to merely registering the presence of the particle. Most detectors utilize in some way the ionization produced when these particles interact with matter. The first question that arises when dealing with particle detectors is the following: why do we need radiation detectors?

In physics, radiation is defined as the emission or transmission of energy in the form of waves or particles through space or through a material medium. This includes:

- Electromagnetic radiation: radio waves, visible light, x-rays, and gamma radiation  $(\gamma)$ ;

- Particle radiation: alpha radiation  $(\alpha)$ , beta radiation  $(\beta)$  and neutron radiation;

- Acoustic radiation: ultrasound, sound, and seismic waves (dependent on a physical transmission medium);

- Gravitational radiation that takes the form of gravitational waves, or ripples in the curvature of spacetime.

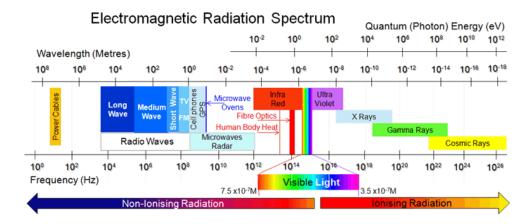

Figure 1.1 shows the radiation spectrum for most commonly encountered types of radiation.

Figure 1.1: Common electromagnetic spectrum.

In general, radiation is categorized as either ionizing or non-ionizing depending on the energy emitted by the radiated particles. In particular, ionizing radiation carries more than 10 eV. Such an energy is enough to ionize atoms and molecules, and break chemical bonds. This is an important distinction due to the large difference in harmfulness to living organisms. A common source of ionizing radiation is radioactive material that emits  $\alpha$ ,  $\beta$ , or  $\gamma$  radiation, that respectively consist of helium nuclei, electrons or positrons and photons. Other radiation sources include X-rays from medical radiography examinations and secondary cosmic rays, such as muons, mesons, positrons, neutrons and other particles. Such secondary cosmic rays are produced after primary cosmic rays interaction with Earth's atmosphere. Gamma rays, X-rays and

the higher energy range of ultraviolet light constitute the ionizing part of the electromagnetic spectrum. On the other hand, the spectrum including visible light, infrared light, microwaves, and radio waves represents the non-ionizing part. The non-ionizing radiation is characterized by lower-energy and longer-wavelength. Its main effect when interacting with tissue is heating. This type of radiation only damages cells if the intensity is high enough to cause excessive heating. Radiation with sufficiently high energy can remove electrons from atoms and create ions. In more details, ionization phenomenon occurs when an electron is stripped from an electron shell of the atom, leaving the atom with a net positive charge. In most of the cases, exposure to ionizing radiation is considered the most important cause of genetic damage, and thus cancer, risk increasing. Indeed, the living cells and specially their DNA can be damaged by the ionization.

Starting from these considerations, is easy to deduct that particle detectors are important devices for personal safety, since ionizing radiation cannot be seen, smelled, heard, tasted, thus is not perceptible. For this reason, routine radiation surveys are required to ensure that radiation exposures are maintained as low as reasonably achievable. In particular this is relevant in such work areas for certain occupations, working with and/or in presence of radioactive materials (mines, cleanup workers, nuclear and medical workers, etc).

However ionizing radiation has many practical uses in medicine, research and construction, but, as explained above, it presents a health hazard if used improperly. As an example, medical diagnostic and therapy procedures used to define and diagnose medical conditions are currently the greatest manmade source of ionizing radiation exposure to the general population. Such a radiation is adopted to generate images of the human body in many types of medical imaging procedures. Indeed, the most common application of a radiation detector is digital imaging: examples of detectors are CCDs or CMOS pixel sensors normally found in digital cameras, which are detectors sensitive to the visible light. These detectors are considered as "pixellated": they are made up of multiple of small elements (pixels), each one acquiring data independently. The resulting image is a data combination acquired by all pixels. The notion of pixel (short for "picture element") has been introduced in image processing to describe the smallest discernible element in a given process or devices. A pixel detector is therefore a device able to detect an image and the size of the

pixel corresponds to the granularity of the image. Nowadays, everyday life is surrounded by pixel detectors. Photo cameras, smartphones and X-ray films are just common examples and follow the same working principle: photons of different energies are integrated over each sensing element (pixel) during some exposure time and generate an intensity distribution which is the image [1]. In general, the image quality is determined by X-ray detector characteristics such as sensitivity, spatial resolution, and depth of field, as well as by the examination time, object contrast, and object intensity. In medical imaging the radiation intensity is always severely limited in the interest of a low radiation dose to the patient.

Sensor designed to detect different kinds of radiations are also used in other applications. One of the environment for which there is need of state-of-the-art detector system is High Energy Physics (HEP). HEP is the science that studies the nature of elementary particles that constitute the matter. Thus, detecting particles produced by collisions in accelerators makes it possible to study the basic constituents of matter. Multiple layers of pixellated detectors are used in modern HEP experiments to track and identify particles passing through them. For this application the pixel detectors are now widely used and they constitute a fundamental part of the HEP experiments operating at the most powerful particle accelerators in the world.

Another important application for novel detectors is also space science. In particular, pixel detectors are used for optical and X-ray astronomy and for planetary and solar science. Cameras or imaging devices are often mounted on satellites, both for space and Earth observation. An example in which a radiation sensor can be used in space is as a dosimetry device for astronauts, in order to measure their exposure to potentially harmful radiation [2]. Technology developed for space and HEP applications, especially for X-ray imaging, can be applied in other fields too. The main particular field of application is medical imaging, where pixel detectors are one of the fundamental components of systems for Computed Tomography, Positron Emission Tomography (PET) and other diagnostic techniques.

In general, early detectors used photographic plates to detect the tracks left by nuclear interactions. Moreover, the cloud chambers, used to discover subnuclear particles, needed photographic recording and a demanding measurement of tracks from the photographs. Advances in microelectronics, particularly in integrated silicon technology over the last decades permitted significant progress in all field of engineering and science, specially for radiation detection. Moreover, advances in materials, particularly ultra-pure materials, and methods of fabrication have been critical to the creation of new and better detectors. The development of new ways of designing circuits ever smaller, with good resistance to damaging radiation favored several progresses in large-scale experiments.

#### 1.2 Main challenges

One of the main requirement of a detector system is to being able to reliably work in the operational environment described above. For many applications (space, most of HEP experiments) it means that the electronics must be able to cope with a highly radioactive environment, since it can cause damage to the devices or sudden failures. Other challenges include meeting the requirement on the accuracy of the measurement. One of the most important parameter is the resolution, evaluated as spatial, energy and time resolution. In order to achieve a high spatial accuracy the detector must feature small pixels, so that the pixel matrix has a smaller pitch. The demand for smaller pixels requires the use of newer downscaled CMOS technologies. Other important characteristics for many applications are the speed of the front-end and the dynamic range of the detector. The first one represents the number of particles that can be detected in a unit of time, whereas the second one is the range of particle energy that can be correctly detected by the system. Improvements in the technology, together with smaller pixels, opened the possibility to develop "intelligent" system, able to implement advanced features. Some of the capabilities that can be included are calibration circuits, on-chip data processing or error correction algorithms. Implementation of such intelligent systems comes, of course, at the cost of additional complexity and power consumption. In many different applications a high power consumption has to be avoided, since heat dissipation can be problematic in some conditions. In space, for example, detectors may be used in an airless environment, which reduces the cooling possibilities. In HEP experiments a cooling system may interfere with the measurement being performed, due to a requirement on material budget. Novel techniques allowing

to reduce the power consumption are thus needed.

#### 1.3 The operating principle

In order to design a radiation detector, different architectures can be used and are suitable to many applications. One of the main difference between semiconductor detectors is the way they measure the charge deposited by particles, by integrating it over time or by counting single events. In both systems charge is produced by the interaction of a particle with a material layer that can produce electron-hole pairs when exposed to radiation.

In integrating systems the charge is collected in an analog front-end and integrated over time. Currents generated by other sources (such as leakage currents) are also integrated, producing a noise signal. The amount of charge collected in a specific acquisition time is then stored, measured and read out. An event counting system, on the other hand, compares the collected charge with a threshold to detect single events. If the charge is above the preset threshold a counter is incremented, otherwise the signal is discarded. It also makes it possible to perform additional measurements such as acquisition of the arrival time. Moreover, multiple thresholds can be employed to discriminate particles which different deposited charge. This permits their identification. The main disadvantage of such systems compared to integrating devices is that the system must be ready to acquire a new particle after detecting one. This limits the number of particles that can be detected if they arrive at a high rate. Detection systems can also be divided in different categories according to the technology used for charge collection. As an example, the two main technologies for pixel detectors used for HEP applications are mentioned here, but there are many others used in other environments. One way of collecting charge is using the Monolithic Active Pixel Sensors (MAPS) approach. These devices incorporate in the same substrate a thin layer of sensitive material that generate electron-hole pairs interacting with incoming particles. Meanwhile they include the readout electronics, which can be built using standard CMOS technology.

The other main technology used for radiation detectors is the *hybrid pixel* detector architecture. In this kind of detector, the readout electronics is built separately from the sensitive material. The sensor is divided in pixels with

the same pitch as the readout chip and both are connected together. Since the two parts are produced separately, they can be optimized and designed independently from each other. Indeed, any standard CMOS technology can be used to design the readout electronics. The improvements in the lithographic process can be exploited to develop advanced systems, with smaller dimensions and more peculiar features. The main disadvantage of this architecture is the cost of the manufacture process, especially for pixel detectors with very small dimensions.

# Portable Radon detection system

#### 2.1 Introduction

The advent of silicon photomultipliers in radiation detection has enabled designing systems with characteristics not achievable with conventional photomultiplier tubes available in the past. Several agencies in the world have classified Radon as a human carcinogen and have demonstrated a correlation between environmental Radon concentration and lung cancer risk. Radon dosimetry supplies valuable information about radioactive health risks in indoor environments. The activity reported along with this chapter concerns the development of a compact system with compatible capabilities to the commercial Radon detectors state-of-art. The device is able to detect real-time indoor Radon concentration and to monitor environmental data, providing a reliable value of Radon concentration within few hours. Such detector could have multiple uses in research and industrial applications. The developed system, with embedded processing and wireless communication capabilities, is based on a scintillator coupled to a Silicon Photomultiplier, low cost read-out electronics and system ventilation.

#### 2.2 Motivation and Outlines

Several agencies in the world, including the World Health Organization (WHO) and the International Agency for Research on Cancer (IARC), have already classified Radon as human carcinogen and have demonstrated a correlation between environmental Radon concentration and lung cancer risk.

Radon (<sup>222</sup>Rn) is a colourless, odourless, tasteless radioactive gas that comes from granitic or shale related areas in the ground. It can often be sourced by granite floors materials or even from construction materials, thus polluting indoor air [3]. Radon was identified as a human lung carcinogen in 1986 by the WHO [4]. According to this organization, Radon gas is by far the most important source of ionizing radiation among those that are of natural origin. The carcinogenetic nature of such a gas is due to the fact that the element is an alpha source. The alpha particles readily stop (i.e. deposit all of their energy) in human tissue. Most of the inhaled Radon gas is immediately exhaled, however, if decay occurs in the lungs, the resulting solid radioactive particles can settle onto bronchial epithelial cells causing DNA damage. This gas constitutes the first cause of lung cancer deaths among non-smokers in the United States, and the second for smokers. Each year in the US there are an estimated 20000 deaths from lung cancer. In particular, recent epidemiological studies of the International Commission on Radiological Protection (ICRP), report an increased risk of lung cancer onset of at least 8\% for a concentration equal to 100 Bq/m<sup>3</sup>, considering an exposure period that can vary between 5 and 30-35 years, before the disease diagnosis [5]. It is a significant source of radiation exposure to the population and, in some situations, it may be the main source in the working environment. The exposure levels, however, greatly vary depending on the territorial geology, the type of buildings, their ventilation and their behavior occupants. Just to show some numbers concerning the situation in Italy, Lombardy region has a higher concentration of indoor Radon (116 Bq/m<sup>3</sup>) than the national average (70 Bq/m<sup>3</sup>). In particular, the Province of Bergamo, along with that of Sondrio, has the highest concentration. The problem is a deep concern for Regional and State Institutions. In fact, at the end of 2011, Lombardy Region has issued the Decree number 12678 containing the subject: "Guidelines to prevent Radon exposure within indoor environments" [6]. It is now an established fact

that high Radon concentration in the buildings may pose a significant risk of lung cancer to the people living there [7]. For this reason, indoor Radon detection can be used to assess the radioactive health risk in a given place [8]. Furthermore, outdoor detection can be useful in mining to detect concentrations of Uranium as well as for earthquakes prediction studies [9, 10]. In all these applications, portability is a key feature for the detector. A more detailed overview on commercial Radon detectors will follow in the next paragraphs.

#### 2.3 Origins of Radon

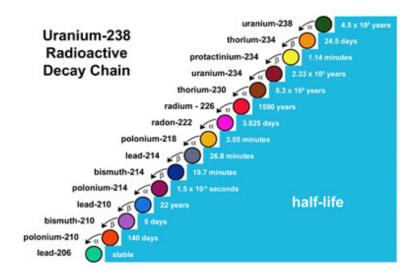

Radon is generated in the decay chain of <sup>238</sup>U, the most common Uranium isotope at 99.284% abundance in uranium ore. The isotope has a very long half-life, about 4.5 billion years. It decays to the stable element <sup>206</sup>Pb through a long decay chain depicted in Figure 2.1.

Figure 2.1: Uranium decay chain

Many branches in the chain decay via alpha or beta emissions, but <sup>222</sup>Rn is the first gaseous element with a short 3.8 days half-life, decaying via 5.6 MeV alpha emissions. These characteristics make Radon a health concern: it can propagate, accumulate areas with little ventilation and, finally, can be breathed into the lungs. Clearly, the abundance of Radon is strongly dependent on the geology. In fact, its concentration shows strong geographical variations: generally a strong presence is found in granitic or shale formations, while lower

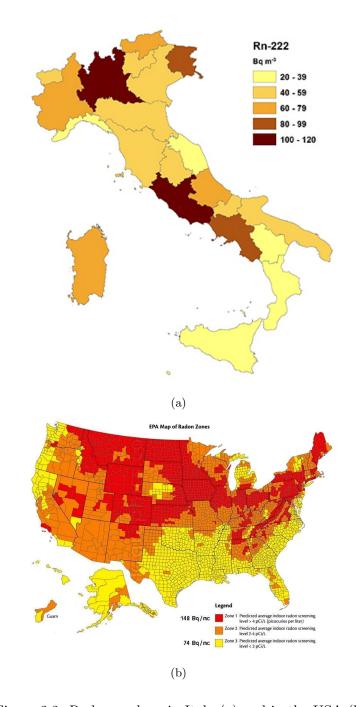

concentrations are found in water and sandy soil. Figure 2.2 shows the Radon geology in Italy and in the United States. Typical Radon concentrations are in the 1 pCi/l (or 0.037 Bq/l). From health physics studies, the threshold of concern for Radon concentrations has been set by the Environmental Protection Agency (EPA) to 4 pCi/l (or 0.148 Bq/l).

Fortunately, Radon mitigation for the home is rather simple and inexpensive. If a high Radon concentration is found in a house, simple improvements in ventilation will quickly fix the problem. For this reason, agencies recommend that all dwellings be periodically tested for Radon, and if high levels are found, to provide mitigation. Hence, Radon testing is very important. There are several ways homes can be tested for Radon. Testing methods vary from using activated charcoal sponges that trap Radon atoms, to optical detection of alpha tracks in plastic films. In these cases, a specimen is sent to a laboratory for analysis. There are even monitoring methods based on alpha particle spectroscopy and counting. These processes allow for real time measurements of concentrations directly in-situ. A comprehensive description of the techniques and methods is given in the following paragraph.

#### 2.4 Measurement techniques for Radon detection

Nowadays many different techniques are available for such a type of application. The main difference is found in the nature of the measurement. A first family of measurements requires some form of sampling into a removable material and a successive laboratory analysis. The classical method consists in a so-called "grab sampling". This technique exploits capturing different samples obtained by filtering air at a test site through a charcoal filter at various time slots. The samples are then analyzed in a laboratory by a gamma spectrometer. It is a typical testing procedure: it represents what happened cumulatively in a certain time frame, and it gives no indication if the concentration values were seen as constant during a certain period or if they were due to a spike during the collection time. For these techniques the typical collection times can be as high as several months. In other words, this type of measurement gives a worst-case scenario, and identifies the total Radon dose a person would have received if he/she stayed in the environment for the whole duration of the collection campaign. Often it is more indicative to have a measurement of how

Figure 2.2: Radon geology in Italy (a) and in the USA (b)  $\,$

a concentration changes as a function of time, as it represents a real scenario. For these purposes, the second family of measurements allows continuous monitoring of the concentrations, so it is possible to establish patterns and relations between concentrations and other factors. Devices belonging to this second family are also known as continuous area monitors (CAM). The principle behind CAM devices is rather simple, as they are mostly based on alpha counting. Alpha particles are a very detectable form of radiation, and the detection can be performed via gaseous, liquid or solid state detectors (both semiconductor or scintillation-based). In fact, there is a great variety of CAM detectors [11]. Nowadays the detection is performed by in-field alpha spectroscopy or passive closed-end cup devices based on polycarbonate detector material, such as PADC or CR-39 [12]. Sensing elements are sealed ionization chambers or surface barrier semiconductor diodes with a sufficiently thin active surface. The alpha particles impinging on the surface will pass the barrier and deposit their energy in the depletion region of the diode. Carefully manufactured diffusion junction diodes have also been proposed [10]. Other devices exploit internal signal amplification based on the bipolar transistor (BJT) effect that can be efficiently used for alpha-ray detection [13]. The main disadvantage is that reliable Radon concentration values are given after days or weeks. It is now an established fact that high Radon concentration in the houses may pose a significant risk of lung cancer to the people living there. Studies from all over the world show that a well-planned and systematic measurement of indoor Radon concentration is necessary to calculate the actual dose received upon indoor Radon concentration exposure. Depending on how air enters the measurement volume, some detectors may be faster than others. In any case, CAM detectors tend to be expensive (several hundreds to thousands of dollars), while the simpler accumulation-based detectors cost only a few tens of dollars (although the laboratory analysis may make up for the cost difference).

In adopting SiPMs and a scintillator as detector elements, it is possible to reduce system costs quite significantly: SiPMs are devices based on well-established silicon processes normally used for making integrated circuits. This is not true for devices such as silicon barrier diodes, as the purity levels required are not compatible with integrated circuit technologies. Further details on SiPMs structure will be presented later in the next paragraphs. In addition, in recent years several studies have been made in relation to the effect of

different parameters on the detected level of indoor Radon. In fact, the Radon concentration and its decay products in dwellings show large temporal and local fluctuations due to the temperature, pressure, humidity, building material, ventilation condition, wind speed, etc [14].

#### 2.5 System requirements and goals

Some reasonable requirements for the proposed Radon detection system have been established and major constraints have been identified. These are reported in the following paragraph.

As previously stated, the EPA recommends that all dwellings be periodically tested for the presence of Radon. First of all, two main requirements can be established: the Radon detection system should be as portable and affordable as possible. Periodical testing means that the instrument may be utilized either as a continuous monitor or to make measurements only periodically. Therefore it is unthinkable to baseline an instrument that takes more than a few 100 cm<sup>3</sup> of space and requires constant maintenance (such as battery replacement or continuous calibrations). Thus, more requirements are identified: the device must be as maintenance free as possible, and even must be able to function for a long period of time without needing special attention. Currently, the standard Radon measurement requires the measuring device to be left unattended and undisturbed in an area for at least two days. This is due to the fact that in order to reach the statistical significance needed to complete a measurement, a certain number of events have to be collected. Given the activity related to typical Radon concentrations (pCi/l), this is accomplished in the time indicated above. If there were a way of increasing the number of events per unit time, there would be no other reasons why the measurement could not take less time. This is another important point: finding a technique that allows for quicker collection times. The practical impact on the system design is not only obvious time savings, but also less stringent requirements on how long the instrument must be able to operate on its own power source.

An initial set of specifications can be compiled. The application requirements and how they translate into system design considerations can be summarized with the following points:

• Portability: total size and weight constrained and low power;

- Cost: choice of inexpensive detector and electronics;

- Ease of operations: functions without operator intervention or maintenance;

- Measurement duration: shorter than two days for conventional applications:

In more details, portability means that the instrument cannot be heavy, its size must be contained and must possess its own internal power source. Commercial systems are available in several form factors, depending on the underlying principles and the performance level. The simplest traditional monitors are comparable to standard smoke detectors in size and weight; they offer limited performance (the reading levels become statistically significant after an average of 7 days) with a cost equal to about 150 Dollars. Professional systems are larger and heavier (4000 cm<sup>3</sup> and 1 kg) and cost in the order of 1000 Euros, but it offer the possibility of completing measurements within 48 hours. Recently, new Radon detector designs have hit the market. They are targeted to homeowner at costs of about 200 Euros. The weight is only 130 gr and can execute measurements at 2.7 pCi/l with a 20% precision in one week or 10% in a month. As an example, RSens (www.rsens.it) is an innovative Radon gas sensor battery-powered and easily programmable, with small size (16x16x11 cm) and 1.8 Kg of weight, that has achieved success during the last few years. It can carry out Radon measurements with 6% accuracy after 48 hours (with a concentration of 150  $Bq/m^3$ ). There is clearly room for a comparable-sized device capable of measuring similar concentrations in a few hours at comparable cost. Therefore it is possible to set a goal for a new design to be in the few hundreds cm<sup>3</sup>, weight a few hundred grams and cost a few hundred of Euros.

Adopting a right technology is important in order to reach such goals. First of all, a simple scenario where air is introduced into a predetermined volume is examined. Such an assumption is without even considering which detector is going to be used. Furthermore, the other hypothesis done is that all of the decays within the volume can somehow be detected. The mitigation threshold is set at 4 pCi/l by EPA, and the unknown variable is the required time to detect 1/10th of such activity as a function of measurement volume. Since 0.4

pCi corresponds to 0.0148 Bq (or 0.0148 decays per second), table 2.1 indicates how many decays per second take place in a given volume.

| Volume [liters] | Decays per second |

|-----------------|-------------------|

| 0.1             | 0.00148           |

| 0.5             | 0.0074            |

| 1               | 0.0148            |

| 1.5             | 0.0222            |

| 2               | 0.0296            |

| 2.5             | 0.037             |

| 3               | 0.0444            |

Table 2.1: Number of decays per second in different volumes for a specific activity of  $0.4~\mathrm{pCi/l}$ .

If, as assumed above, all particles are detected, it is possible to count, for example, 3 events every 20 liters of air. On the other hand, the number of events detected as a function of time can be calculated (see table 2.2). This is done assuming that the entire volume of air every second can be recycled and keeping the activity constant.

| Times [s] | Decays in 0.1 l/s | Decays in 1 l/s | Decays in 3 l/s |

|-----------|-------------------|-----------------|-----------------|

| 1         | 0.00148           | 0.0148          | 0.0444          |

| 2         | 0.00296           | 0.0296          | 0.0888          |

| 5         | 0.0074            | 0.074           | 0.222           |

| 10        | 0.0148            | 0.148           | 0.444           |

| 20        | 0.0296            | 0.296           | 0.888           |

| 50        | 0.0740            | 0.740           | 2.22            |

| 100       | 0.148             | 1.48            | 4.44            |

| 200       | 0.296             | 2.96            | 8.88            |

| 500       | 0.74              | 7.4             | 22.2            |

| 1000      | 1.48              | 14.8            | 44.4            |

| 2000      | 2.96              | 29.6            | 88.8            |

| 5000      | 7.4               | 74              | 222             |

| 10000     | 14.8              | 148             | 444             |

Table 2.2: Total events for a 0.4 pCi/l of volume exchange.

Since these are radioactive decays, they are subject to Poissonian statistics

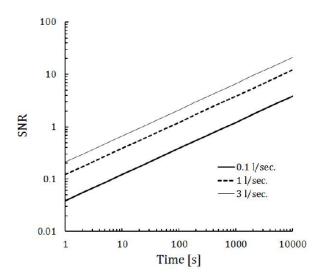

Figure 2.3: Signal-to-noise ratio for different flows at a 0.4 pCi/l activity

which determines that the total uncertainty on a number of events N is  $N/\sqrt{N}$ . Therefore, the plot shown in figure 2.3 represents a signal-to-noise ratio defined as the inverse of the uncertainty. From the plot it is visible after how long a unity SNR is reached, or how long an acquisition should last in order to achieve a certain SNR. For example, at 1 l/s an SNR of 10 (or a 10% variance) can be reached in less than 10000 seconds, corresponding to less than 3 hours. The important conclusion in this case is that there are no obvious physics reasons why a good detection would require more than few hours. This is, of course, a rough estimate: in a real system only a fraction of the decays is actually collected by a detector. By refining the estimate however, it is easy to determine the ultimate limits of such a technique.

#### 2.6 Detector and Front-End design

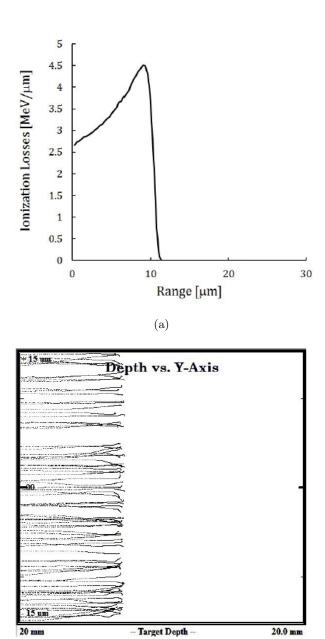

The choice of the detector will determine what fraction of the total events is collected within the volume. In fact the detector establishes, along many other things, most geometrical constraints. In order to operate this choice correctly, it is useful to consider the main properties of alpha radiation. It is composed by helium nuclei (2 protons), therefore it is quite massive. It will tend to stop within short distances inside materials. Figure 2.4 shows a typical Bragg curve

Figure 2.4: Typical Bragg curve for 5.49 MeV alpha particles in air.

for 5.49 MeV alpha particles in air. The peak, known as Bragg peak, is a pronounced peak on the Bragg curve which plots the energy loss of ionizing radiation during its travel through matter. It is dependent on the absorber and the particle characteristics. The most important observation about the Bragg peak is that at the peak there is the highest energy transfer between the particles and the absorber. The Bragg peak occurs at about 3.8 cm. This means that the measurement volume does not have to be too deep beyond 3-4 cm: anything beyond that will only contribute to losses of useful events.

Besides reasonable limits to the detector, size and type do not depend on physical limitation to the surface area of the detector, but on design constraints. Having established this, there is clearly no physical limitation to the surface area of the detector. These limitations are practicality in obtaining certain sizes, cost of the material and of related sensors (such as SiPMs if a scintillator is used). For cost reasons, for this prototype scintillators are used because they usually are inexpensive. Therefore, not to alter the measurements, the detector of choice has to be blind to other radiation (gamma, neutron). For similar reasons, it is good to limit the surface area to about 2.5 cm<sup>2</sup> in order to avoid costly choices and unnecessarily growing overall system size. A quick literature survey indicates that the ideal solution is one of the very first scintillators used in alpha spectroscopy (since the 1930s): zinc-sulfide silver activated. This material has practically no sensitivity to gamma rays or neutrons (unless activated with elements that have finite neutron cross-section). It is available as polycrystalline powder that, with the appropriate binders, can be painted

on a transparent backing (usually Mylar) with the thickness of choice. The interesting thing is that the detection efficiency for alpha particles (as measured by detected particles/incident particles) is nearly 100% for thicknesses between 10  $\mu$  m and 30  $\mu$ m [15]. The only drawback for this material is the fact that it is not completely transparent due to its polycrystalline form, and its refraction index is high (2.4). In any case, given the alpha particle energy (5.6 MeV), the overall brightness of the events will be sufficient. ZnS(Ag) is readily available from scintillator manufacturers in sheets measuring 216 mm x 279 mm. Its trade name is EJ-440. The scintillator is deposited on a clear plastic sheet that serves as coupling mechanism to a PMT window or to a SiPM. The thickness of the deposited layer is chosen to optimize alpha particle detection (thus, as mentioned above, it is between 10 and 30  $\mu$ m). The following table (2.3) supplies a list of the common constants for such a scintillator.

| Parameters                     | Values                  |

|--------------------------------|-------------------------|

| Light Output (% of Anthracene) | 3                       |

| Peak Emission Wavelength       | $450~\mathrm{nm}$       |

| Decay Time                     | 200  ns                 |

| Density                        | $3.25~\mathrm{mg/cm^2}$ |

| Polyester Film Thickness       | $0.25~\mathrm{mm}$      |

| Refraction Index               | 2.4                     |

| Cost                           | $1  \text{/cm}^2$       |

Table 2.3: Main characteristics of the scintillator ZnS(Ag) on Mylar backing.

It is common referring to Anthracene to measure light output of certain scintillators. The light output for Anthracene is 17.400 photons/MeV. A complete datasheet is available from [16]. The low cost of this scintillator clearly does not drive the choice for its size. This will be determined by the cost of the light readout. The cost for cm<sup>2</sup> of PMTs and a SiPMs is quite comparable, with the outlook for SiPMs to become much cheaper in the near future. It is therefore worth to take advantage of the benefits offered by the latter. Before deeply going in the description of the detector model, a brief explanation of SiPMs working principles is given in the followings.

The radiation detection via scintillation light involves very low levels of light. Thus, the photosensor has to be either very efficient, or provide internal gain,

Figure 2.5: Simplified schema of a silicon photomultiplier.

so that the charge photogenerated is amplified to obtain high signal-to-noise ratio (SNR). Photodiodes (PDs) have high quantum efficiency but they have some shortcoming such as no- to modest gain, so that the instrumentation design is complex due to poor SNR. Photomultiplier tubes (PMTs) have very high gain, about 10<sup>6</sup>, but they are bulky, fragile and require high voltages in the order of kilovolts. In the late 90s a new device was envisioned that could offer the high gain of PMTs and some of the advantages of Silicon photodetectors. Such devices are known as Silicon photomultipliers (SiPMs in short). These devices are based on small (about 10  $\mu$ m-sized) elementary cells that respond to a single light photon through an avalanche effect in a very similar way to Geiger-Muller counters. If several such elementary cells are constructed on a larger area, they are able to detect the energy deposited in the scintillator in a proportional way. Each cell is pratically a photodiode and a quench resistor in series to limit the discharge current. The photodiode operates a few volts above its breakdown voltage so that electrical breakdown occurs if a photoelectron is generated within the active volume. In order to be sensitive to successive photons every avalanche breakdown is interrupted by the built-in quench resistor. Relevant SiPM properties are low operating voltage (usually lower than 100 V), ruggedness, insensitivity to magnetic fields as well as compact dimensions [17]. Figure 2.5 shows a simplified structure of a silicon photomultiplier.

The market offers several SiPMs in the few cm<sup>2</sup>. For the detector proposed

Figure 2.6: SensL Array SB-4, silicon photomultiplier.

a 4x4 array of 9 mm<sup>2</sup> cells has been chosen from SensL (model: Array SB-4). The cost is about 400 dollars in small quantities. The array, depicted in Figure 2.6, is conveniently mounted on a low-profile ceramic carrier with through-hole pins to enable easy design and installation on a PC board. Tables 2.4 and 2.5 show the pixel and whole array characteristics respectively. Data are taken from SensL Array datasheet [18].

The interesting parameters of the SiPM are the Photo Detection Efficiency (PDE) and the peak sensitivity wavelength of 420 nm. The SiPM PDE by definition represents how efficient the device ultimately is in detecting photons. Typical PDE values are about 25% (up to 35%) at 450 nm peak wavelength. The efficiency depends also on over-voltage. The two parameters perfectly match with the scintillator chosen for this application. The SiPM has been coupled to the scintillator sheet via optical grease.

The ZnS(Ag) scintillator has a refraction index of 2.4, and, as mentioned above, it is deposited on a plastic film (n=1.67). Since the SiPM light entry window is encapsulated in clear epoxy (n=1.54), most of the light losses will be concentrated in the ZnS(Ag)/Mylar interface, where the strongest mismatch exists. In fact, from the Fresnel equations for normal incidence, the reflected light at this interface is 18% of the incident light. The remaining optics is coupled with standard silicon-based optical grease such as the Saint-Gobain

| Parameters                    | Values                          |                                 |

|-------------------------------|---------------------------------|---------------------------------|

|                               | Array SB-4                      | SPM42H5-60P                     |

| Pixel area                    | $3.16 \times 3.16 \text{ mm}^2$ | $3.96 \times 4.44 \text{ mm}^2$ |

| Pixel thickness               | $450~\mathrm{nm}$               |                                 |

| Pixel active area             | $3x3 \text{ mm}^2$              |                                 |

| Breakdown voltage (VBr)       | $24.5\pm0.5~\mathrm{V}$         | $28\pm1~\mathrm{V}$             |

| Overvoltage range             | 1  to  5  V                     | 1  to  5  V                     |

| Microcell recovery time       | 130  ns                         | 78 ns                           |

| Peak sensitivity wavelength   | $420~\mathrm{nm}$               | 400  nm                         |

| Gain                          | $3x10^{6}$                      | $6.94 \text{x} 10^6$            |

| Number of cells per pixel     | 4774                            | 4871                            |

| $\operatorname{PDE}$          | 31 %                            | 37~%                            |

| Dark current                  | $2.8~\mu\mathrm{A}$             |                                 |

| Temperature dependence of VBr | $<$ 20 mV/ $\rm C$              |                                 |

Table 2.4: Pixel characteristics: comparison between the SensL Array SB-4 and STMicroelectronics SPM42H5-60P.

| Parameters     | Values                                          |

|----------------|-------------------------------------------------|

| Active area    | $13.4\mathrm{x}13.4~\mathrm{mm}^2$              |

| Pixel pitch    | 3.36  mm                                        |

| Package size   | $15.81 \ \mathrm{x} \ 15.31 \ \mathrm{mm}^{-2}$ |

| Package height | $1.5~\mathrm{mm}$                               |

| Package type   | Alumina $Al_2O_3$                               |

Table 2.5: Full array characteristics for the SensL Array SB-4.

BC-630 [19] with a refraction index of 1.47. This is a standard material, widely used in the field. With these choices, the total amount of light transmitted through the interfaces is shown in Table 2.6. For every MeV of incident energy it has been assumed that 52200 photons are generated within the scintillator (see table 2.3) and 50% of them reach the scintillator exit window in the direction of the SiPM. Furthermore the scintillator is supposed to be transparent.

In reality some of the light in the opposite direction bounces back at the ZnS(Ag)/Air interface due to the strong refraction index mismatch for that interface (2.4/1). As can be seen from the table, about 75% (19740 over 26100 photons) of the amount of light in the direction of the SiPM reaches it (or

| Interface                             | $Amplitude \ reflection \ coefficient$ | $Transmitted\ photons$ $[photons/MeV]$ |

|---------------------------------------|----------------------------------------|----------------------------------------|

| ${\rm ZnS(Ag)/Mylar}$                 | 0.179                                  | 21.428                                 |

| Mylar/Bc-630                          | 0.06                                   | 20.143                                 |

| $\mathrm{BC}	ext{-}630/\mathrm{SiPM}$ | 002                                    | 19.740                                 |

Table 2.6: Total amount of light transmitted through the interfaces.

38% of the total, that means: 19740 over 52200 photons). Since the SiPM has a QE of 30% at these wavelengths, about 6000 photoelectrons are generated for each MeV of energy deposited. Each alpha particle (5.6 MeV) will then produce in the worst scenario an average of 33.600 photoelectrons. So in this situation the signal abounds. However, the analysis holds under the assumption that the scintillator is completely transparent. ZnS(Ag) is basically a white polycrystalline powder or paint, therefore its opacity is non-negligible.

A simple experiment has been set up in order to estimate the total losses due to opacity, in particular to estimate the actual light output of the scintillator in response to the 5.6 MeV alpha events. For this purpose a conventional Hamamatsu photomultiplier tube (R11265U-100) was used, coupled with a ZnS(Ag) screen matching the PMT window size (23 mm x 23 mm). The advantages in using a PMT in this case were that the device was readily available and could be integrated immediately with the bench top instrumentation in the laboratory. Such an experiment has been performed by Lorenzo Fabris at Oak Ridge National Laboratory (Nashville, Tennessee). The arrangement is shown in Figure 2.7.

Initially, the PMT was calibrated by coupling it with a CsI(Tl) crystal. By exciting the crystal with a 662 keV <sup>137</sup>Cs source, energy spectra as a function of bias voltage were recorded. By knowing the light output of the crystal and its coupling to the PMT, it was possible to estimate the number of photons that reach the PMT window. The experiment result confirmed that because of opacity, the actual photon yield is about 1000 photons for a 5.6 MeV signal (or about 180 photons for 1 MeV). The influence of opacity is clearly the dominant factor, and reduces brightness considerably. The comforting observation is that, for the energy of interest, the signal is still abundant and many photons can be detected.

Figure 2.7: ZnS(Ag)/PhotoMultiplier setup to measure the actual light output of the scintillator (in photons/MeV).

#### 2.6.1 Detector model

As can be calculated from Figure 2.3, the detector will be enclosed in a measurement chamber in which the air flow is kept at the appropriate rate. Based on the fact that the mean free path of alpha particles in air is in the few cm range (anything beyond that will not contribute to the measurement), the idea is to concentrate the air within a volume that is 1-2 cm deep. In this case, all the alpha particles travel for a distance shorter than the mean free path. In this way, there is a higher chance for the particles to reach the detector. This has been confirmed with Monte Carlo simulation plotted in Figure 2.8.

During this simulation, a 5.6 MeV alpha beam crosses a 2 cm air volume with an absorber at the end. Figure 2.8(a) shows the ionization losses along the path to be about 100 keV/mm. Despite the sharp increase of ionization losses at the absorber, the behavior never incurs the Bragg losses shown in figure 2.4. This confirm that all of the alpha particles emitted within the volume will make it to the detector. A further confirmation of that is shown in Figure 2.8(b) where the direct Monte Carlo simulation output of the alpha tracks is

Figure 2.8: Ionization losses of 5.6 MeV alpha particles in air (a). An absorber is put at a 20 mm distance. Alpha tracks in the same volume of air (b).

visible. A simple integration indicates that all of the alpha particles reach the absorber.

For what concerns the energy distribution within the detector, the particles of interest are mono-energetic at 5.6 MeV. Moreover, the particles reaching the detector will not all deposit the full alpha energy, but also a continuum of lower energies, since each particle loses about 100 keV each millimeter in air. This can be seen from figure 2.8. The resulting energy distribution in the detector will be the overlap of the distributions of alpha particles with a continuum of energy between 5.6 MeV down to 5.6 MeV less the highest possible energy loss in air. Figure 2.9 shows the ionization losses of the alpha particles entering the detector and a zoom into the particle tracks in a region located  $\pm 15~\mu m$  around the incident beam starting at the entrance window of the scintillator (30  $\mu m$  thick). The initial conditions are given by the simulation results of Figure 2.8. From these results it stands out that the energy spectrum collected by the detector is mostly a continuum of energies, without any particular peak.

In order to measure the number of particles that have been detected, the simplest way is to count each event in the detector. This is done by simply counting anything above a predetermined threshold, without energy discrimination. Not requiring energy discrimination in the electronics is an advantageous simplification. The sizing of the chambers cross-section where the SiPM is intended to be placed, has to match the SiPM surface area at a minimum (13.4 x 13.4 mm<sup>2</sup>). Furthermore it could be somewhat larger so that alpha particles from off-axis directions can contribute to the measurement as well, but not so large that the particles are never detected. The measurement volume chosen was thus set to be 26.7 x 26.7 mm<sup>2</sup> for the surface where the detector is mounted, times 17 mm depth. With these dimensions set, is it possible to finally determine how many decays reach the SiPM area. An upper bound can be determined by completely neglecting any alpha particle absorption in air, and observing that the radioactivity of the air within the measurement volume is homogeneous and constant with an activity a (in Bq). The number of particles that hit the photodetector area is proportional to the ratio of the detector area to the total area. In other words, the number of particles hitting the SiPM, N (in particles per second) can be estimated with

Figure 2.9: Alpha particle ionization losses in the detector after transit in the air volume (a). Tracks within the detector (b).

(b)

20 mm

the following fraction:

$$N = a \times \frac{\{\text{SiPM area}\}}{\{\text{total area}\}} = \frac{179.56 \ mm^2}{3251.6 \ mm^2} = 0.055a$$

(2.1)

To confirm this, a Geant4 simulation has been run under the same assumptions, except for the fact that the influence of air on alpha particles was considered. A geometry representative of the measurement chamber was set up and filled it with 1 atm of air with uniform, isotropic emission of 5.6 MeV alphas. The total alpha particles in the chamber resulted to be  $2x10^5$  and the alphas detected in an area equal to the SiPM were 1.3x10<sup>4</sup>. Therefore the calculated fraction of particles reaching the SiPM was 0.065, in good agreement with the geometrical calculations shown above. As already described with the plot of Figure 2.3, the minimum detectable activity is 0.4 pCi/l (one 10th the EPA threshold for remediation). This means 0.0148 Bq within the measurement volume. Considering the value calculated with the equation 2.1 (the least optimistic estimate), the number of decays that will reach the detector every second is 8.14x10<sup>4</sup>. In order to have a 10% precision, the SNR is equal to 10, thus, is necessary to count enough decays to ensure that  $N/\sqrt{N} = 10$ . This means 100 counts, which is easily done in 122.850 s, or 34 hours on average. The result obtained compares very favorably to commercial devices that are currently achieving the same level of precision in one month of continuous measurement. The underlying result is also that a level comparable to the EPA threshold can be detected in just a little longer than 3 hours. It is worth pointing out that, as originally stated, the half-life of radon decays is only 3.8 days, so it is not advisable to simply compress 1 liter of air into the measurement chamber and wait for the evaluation to complete. Designing a simple ventilation system around the measurement volume permits to bypass this potential issue, that allows for a constant air exchange equal to 1 liter per second.

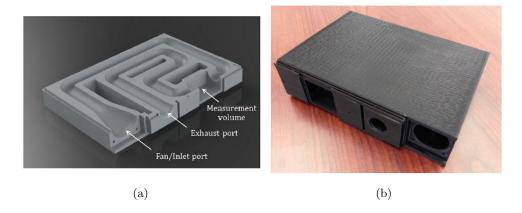

#### 2.6.2 Ventilation system design

There are several small (2.5 cm or so) DC fans capable of low power (less than 1 W) and low rates in the liter per second. Such a fan, coupled with proper air transport, can be used to ensure the desired flow rates within the measurement volume. The SiPMs are light sensitive, therefore precautions must be taken to prevent light from propagating into the measurement chamber. The simple proposed geometry in the model cutout of Figure 2.10(a) could work, provided

Figure 2.10: 3D model section of the tubing system (a). Tubing system developed by 3D printer (b).

the transport losses are kept to a minimum. A fan is connected to the converging duct at the inlet side. The first section of the tube runs into the measurement volume after three right-bends. In this way, any light coming from the outside should be removed completely. The exhaust tube, after the measurement chamber, folds five times before reaching the exit port. The diameter of the tubes is 12.7 mm. It is easy for such a system to estimate the pressure drop along the pipes by using standard calculators (www.pipeflowcalculations.com).

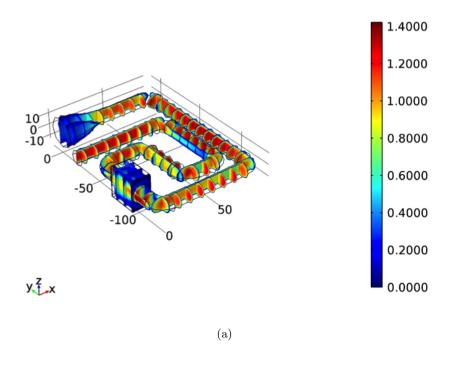

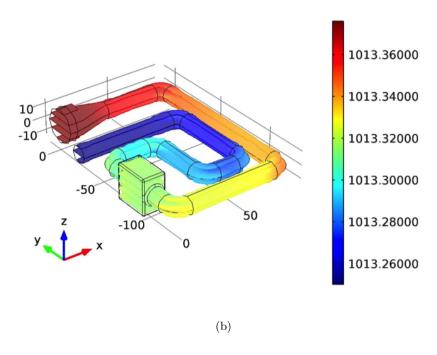

For these simple calculations, losses in elbows can be expressed as equivalent-lengths of pipe from empirical tables or calculators. In this case, the eight elbows and the two sudden enlargements (the measuring volume), are equivalent losses introduced by 370 mm of extra pipe. The overall length of straight pipe is 408 mm as measured on the model. Thus, the pressure losses from inlet to outlet for the whole system are equivalent to those of a 0.5 inch diameter pipe that is 778 mm in length. From the calculation indicated above, the total expected pressure drop for this piping system is about 0.086 mbar. We can safely assume that the overall air flow will be preserved within such system. This calculation has been also verified directly on the model by Computational Fluid Dynamics (CFD) analysis, using Comsol software (www.comsol.com). The total drop pressure calculated as the difference between the pressure value at the ventilation inlet and the outlet is equal to 0.14 mbar. Figures 2.11 (a) and (b) respectively show the outline of the velocity and pressure inside the tube ventilation, in normal condition. The simulations confirm that with such

a pipe system design the flow imposed at the inlet is conserved without major losses. Therefore this confirm to have a simple way of maintaining a constant air flow within the measurement volume.

## 2.6.3 Electronics readout design

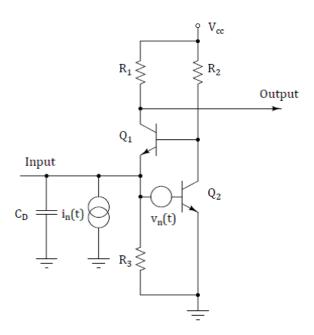

According to the estimation made in the paragraph 2.5, each alpha particle generates about 1000 photoelectrons with a high SNR. The conventional technique for detecting particles is based on the simplest circuit with 50  $\Omega$  resistor to ground. This would match cable impedances and allow for easy handling of the information. However, the resistor will be directly in parallel with the whole 13.6 nF sensor capacitance, introducing a time constant of 50  $\Omega$  x 13.6 nF = 680 ns. Moreover, a fairly long exponential current waveform with an area equal to the total charge produced is expected. The total amount of charge generated by an alpha particle and amplified by the SiPM (assuming a gain of 10<sup>6</sup>), would be 0.16 nC. This mean the voltage drop on the 50  $\Omega$  resistor would have peak amplitude of 11.8 mV. While this may be an acceptable solution in some case, it falls short of two characteristics in this application. First, it is a full-bandwidth signal, so the noise content is expected to be relatively high: it is always good practice to limit the bandwidth to what is really needed. Second, the waveform is highly asymmetrical. This has implications when attempting to identify the presence of an event via counting pulses at a comparator output: the fast edge requires fast triggering circuits. These circuits will respond equally fast to the slow edge, creating possible oscillatory conditions due to the noise present on the tail. A more elegant solution would allow for only as much bandwidth as is needed, a more symmetric waveform, and lower noise. A charge amplifier and a properly designed filter would accomplish these tasks quite nicely, but there would be some complexity due to the high SiPM capacitance. The effect of such a high capacitance on the charge amplifier would be to introduce an undesired bandwidth limitation in a similar way to having the 50  $\Omega$  resistor. The situation could be improved by having more current in the amplifier, but this would mean an increased power demand on the system. Overall, this solution will likely require the use of many components. On the other hand, a current amplifier would offer lower input impedance for a relatively low standing current, making the current waveform more symmetric. In fact, the input impedance of a bipolar transistor in a common base configuration is, to first approximation,

# Slice: Velocità, modulo (m/s) Slice: Velocità, modulo (m/s)

## Slice: Pressure (mbar)

Figure 2.11: CFD analysis for piping ventilation system related to velocity (a) and drop pressure outline (b).

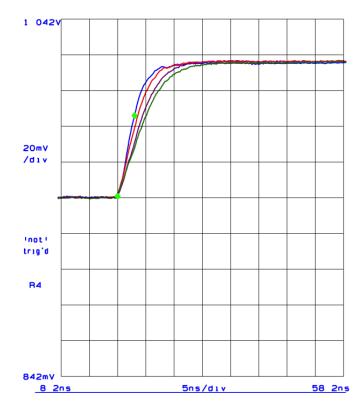

Figure 2.12: First stage of the SiPM readout channel.