University of Bergamo

SCHOOL OF DOCTORAL STUDIES Doctoral Degree in Engineering and Applied Science XXXIII Cycle - SSD: ING-INF/01 - Elettronica

# Design and characterization of a 32 channels mixed-signal processor for the Si(Li) tracker of the GAPS experiment

Thesis advisor: **Prof. Massimo Manghisoni**  Candidate: Mauro SONZOGNI Student ID 1020890

# Contents

| Li | st of l | Figures |                                                                   | v  |

|----|---------|---------|-------------------------------------------------------------------|----|

| Li | st of 7 | Tables  |                                                                   | ix |

| In | trodu   | ction   |                                                                   | 1  |

| 1  | Desi    | U       | P blocks in a 180 nm CMOS technology                              | 3  |

|    | 1.1     |         | e and current reference                                           | 3  |

|    |         | 1.1.1   | Bandgap Voltage Reference                                         | 3  |

|    |         | 1.1.2   | Operational Amplifier                                             | 10 |

|    |         | 1.1.3   | Current Reference                                                 | 12 |

|    |         | 1.1.4   | Resistors choice                                                  | 15 |

|    |         | 1.1.5   | 3-bit Digital to Analog Converter                                 | 17 |

|    |         | 1.1.6   | Current mirrors                                                   | 21 |

|    | 1.2     | 8 bit D | AC for global threshold setting                                   | 25 |

|    |         | 1.2.1   | 8-bit DAC architecture                                            | 25 |

|    |         | 1.2.2   | 4-bit binary-to-thermometer decoder                               | 27 |

|    |         | 1.2.3   | Unary current cell                                                | 27 |

|    |         | 1.2.4   | Threshold voltage generation                                      | 31 |

|    |         | 1.2.5   | Simulations results                                               | 32 |

| 2  | Cha     | racteri | zation of 4 and 8 channels processors for the GAPS Si(Li) de-     |    |

|    | tect    | or read | out                                                               | 35 |

|    | 2.1     | SLIDE   | R4: full analog 4 channels readout ASIC                           | 36 |

|    |         | 2.1.1   | Injection circuit                                                 | 36 |

|    |         | 2.1.2   | SLIDER4 test board                                                | 37 |

|    |         | 2.1.3   | Experimental results                                              | 38 |

|    | 2.2     | SLIDE   | R8: mixed-signal readout processor with 8 channels and digital    |    |

|    |         | back-e  | nd                                                                | 47 |

|    |         | 2.2.1   | Injection circuit                                                 | 47 |

|    |         | 2.2.2   | SLIDER8 digital back-end                                          | 48 |

|    |         | 2.2.3   | Non-self-trigger and self-trigger mode                            | 51 |

|    |         | 2.2.4   | SLIDER8 test board                                                | 53 |

|    |         | 2.2.5   | Characterization Results                                          | 54 |

| 3  | Cha     | racteri | zation of the 32 channels prototype of the flight ASIC for the    |    |

|    | read    | lout of | the GAPS Si(Li) tracker                                           | 65 |

|    | 3.1     | pSLID   | ER32 architecture                                                 | 65 |

|    |         | 3.1.1   | Temperature sensor and detector leakage current readout circuit . | 68 |

|    |         | 3.1.2   | Injection circuit                                                 | 71 |

|    |         |         |                                                                   |    |

## Contents

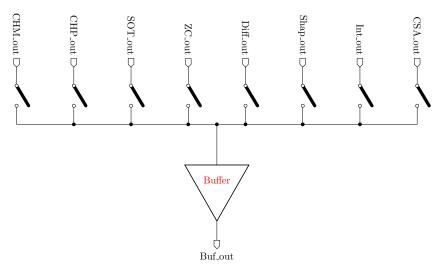

|         | 3.1.3    | pSLIDER32 digital back-end                | 71  |

|---------|----------|-------------------------------------------|-----|

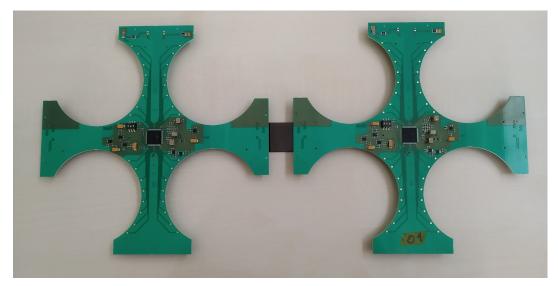

| 3.2     | pSLIDE   | ER32 setup and front-end board            | 74  |

|         | 3.2.1    | Test board                                | 74  |

|         | 3.2.2    | Front-end board                           | 75  |

| 3.3     | Analog   | Measurements                              | 77  |

|         | 3.3.1    | CSA                                       | 77  |

|         | 3.3.2    | Shaper                                    | 77  |

| 3.4     | Digital  | Measurements                              | 79  |

|         | 3.4.1    | Waveform Scan                             | 80  |

|         | 3.4.2    | Input-output channel trans-characteristic | 83  |

|         | 3.4.3    | Pedestals                                 | 85  |

|         | 3.4.4    | Threshold Scan                            | 88  |

|         | 3.4.5    | ENE                                       | 91  |

|         | 3.4.6    | Self-trigger mode                         | 93  |

|         | 3.4.7    | Temperature sensor measurements           | 94  |

|         | 3.4.8    | Leakage current measurements              | 94  |

| 3.5     | Six from | nt-end boards measurements                | 96  |

|         | 3.5.1    | Power supply level and consumption        | 96  |

|         | 3.5.2    | Waveform Scan                             | 99  |

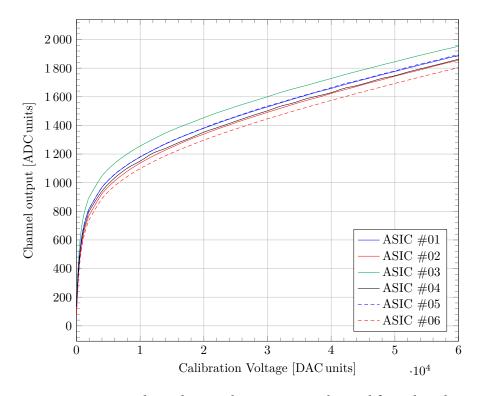

|         | 3.5.3    | Input-output transfer function            | 99  |

| Conclus | ion      |                                           | 103 |

| Append  | ix       |                                           | 105 |

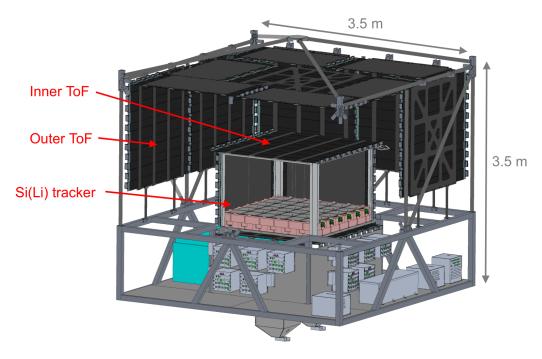

| А       |          | APS experiment                            | 105 |

|         | A.1      | The Dark matter unsolved issue            |     |

|         | A.2      | GAPS experiment                           | 107 |

|         | A.3      | GAPS tracking system                      |     |

| В       | GAPS f   | front-end                                 |     |

| Bibliog | raphy    |                                           | 117 |

# **List of Figures**

| 1.1  | block diagram of GAPS voltage and current references.                          | 3   |

|------|--------------------------------------------------------------------------------|-----|

| 1.2  | bandgap voltage reference schematic.                                           | 5   |

| 1.3  | bandgap voltage reference $V_{ref}$ corner values. Results for corners TT, FS, |     |

|      | and SF cannot be distinguished since they are perfectly superimposed           | 8   |

| 1.4  | Start-up circuit for the Bandgap Voltage Reference.                            | 9   |

| 1.5  | Operational amplifier schematic.                                               | 10  |

| 1.6  | Small signal model of the first stage of the operational amplifier             | 11  |

| 1.7  | Small signal model of the second stage of the operational amplifier.           | 12  |

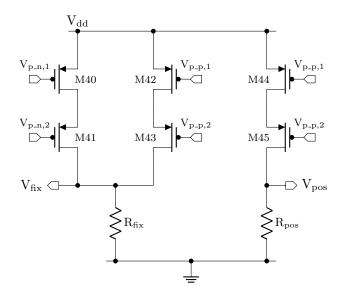

| 1.8  | Semplified schematic of the current generator design for GAPS Front-end.       | 13  |

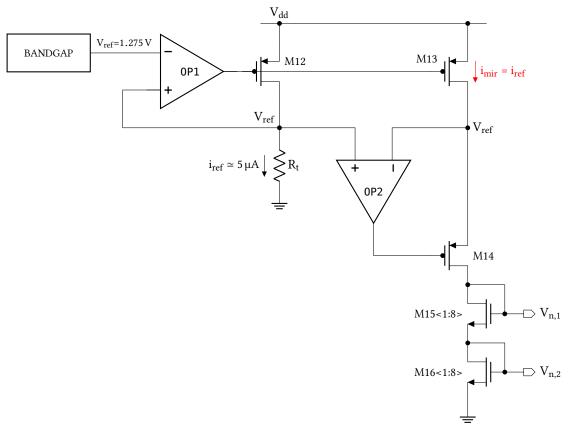

| 1.9  | Current generator schematic.                                                   | 14  |

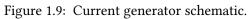

| 1.10 | values of current $I_{mir}$ with respect to $I_{ref}$                          | 14  |

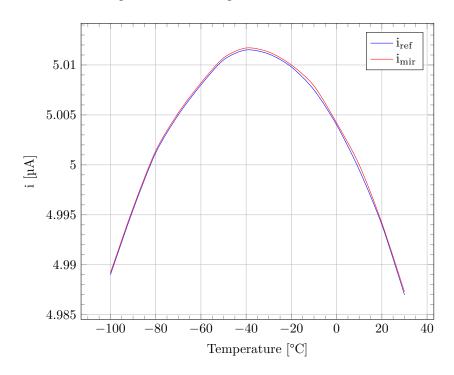

| 1.11 | current reference layout.                                                      | 16  |

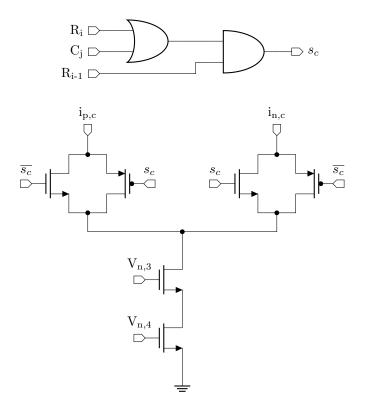

| 1.12 | 3-bit DAC schematic.                                                           | 19  |

| 1.13 | current reference and 3-bit DAC layout                                         | 19  |

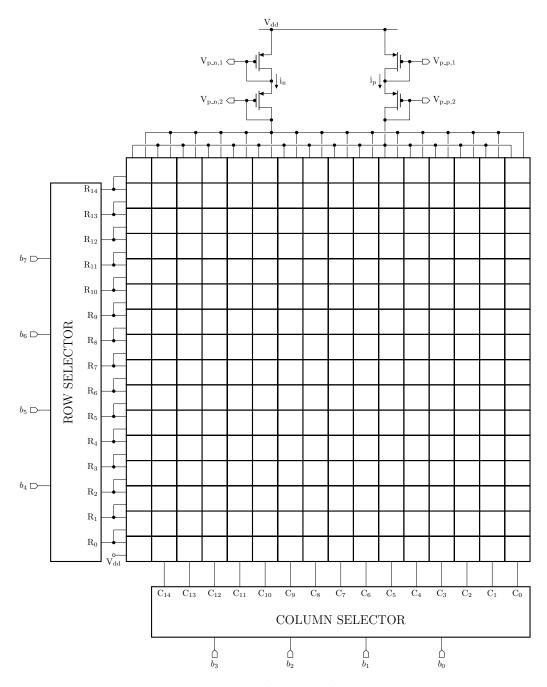

| 1.14 | 8-bit DAC schematic.                                                           | 26  |

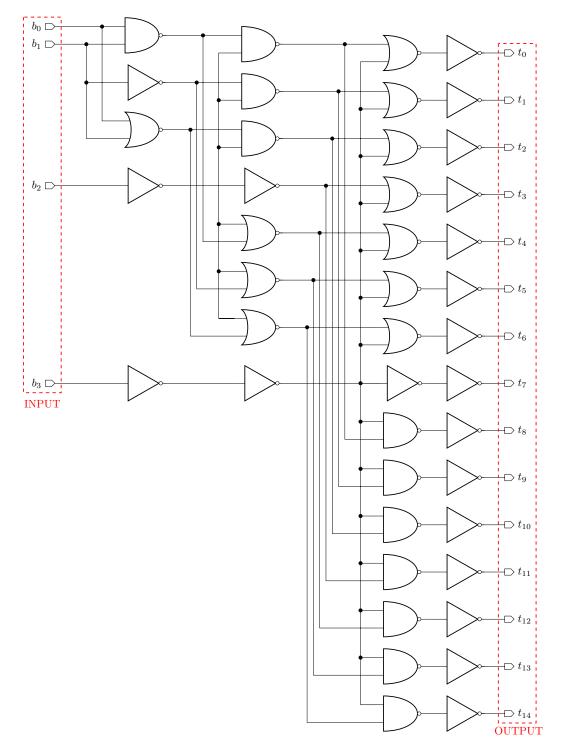

| 1.15 | 4-bit binary-to-thermometer converter.                                         | 28  |

| 1.16 | schematic of the 8-bit DAC cells.                                              | 29  |

| 1.17 | unary current cell layout.                                                     | 30  |

| 1.18 | schematic of the current-to-voltage converter.                                 | 30  |

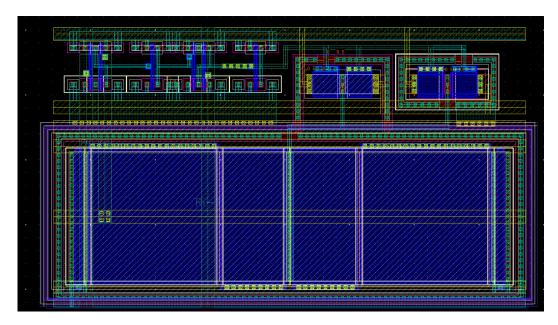

| 1.19 | 8-bit DAC layout.                                                              | 32  |

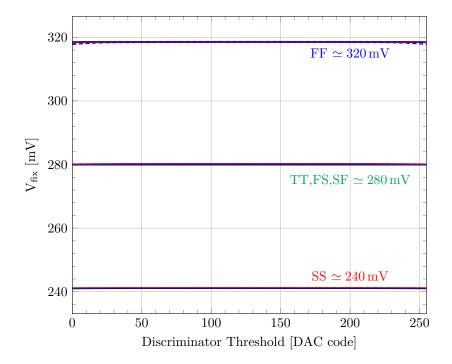

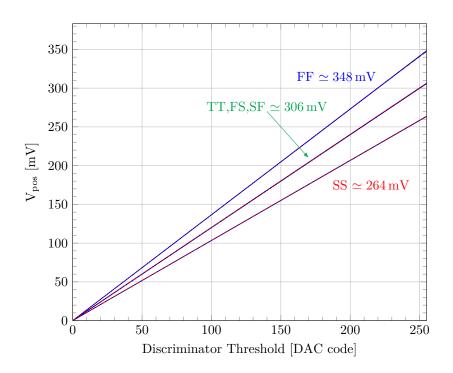

| 1.20 | $V_{fix}$ as obtained by varying process parameters, temperature and supply    |     |

|      | voltage.                                                                       | 33  |

| 1.21 | $V_{pos}$ as obtained by varying process parameters, temperature and supply    |     |

|      | voltage.                                                                       | 33  |

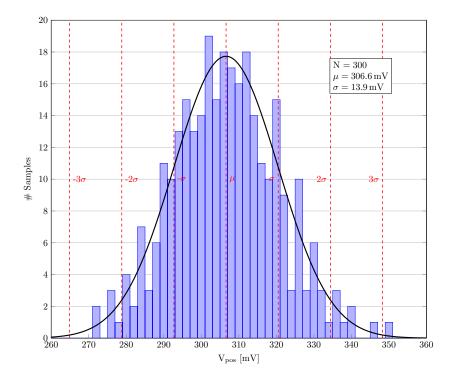

| 1.22 | $V_{pos,max}$ process simulations with a temperature of $-40$ °C and $1.62$ V  | ~ . |

|      | supply voltage                                                                 | 34  |

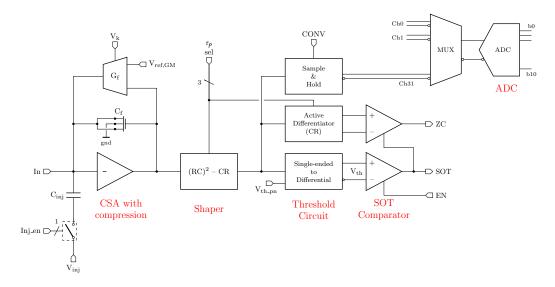

| 2.1  | front-end channel schematic.                                                   | 35  |

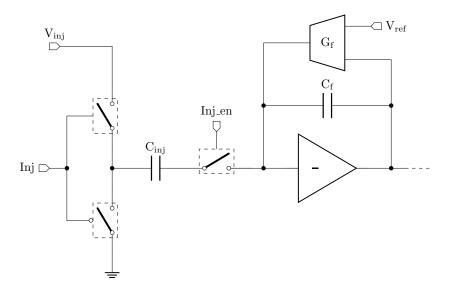

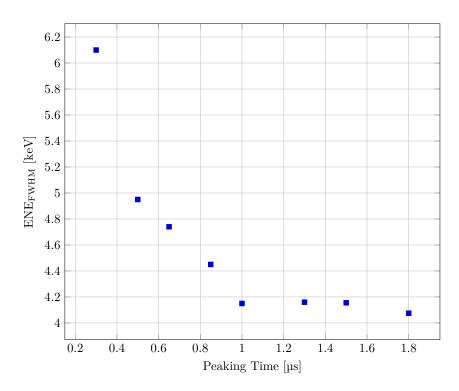

| 2.2  | injection circuit used to test SLIDER4 channel.                                | 36  |

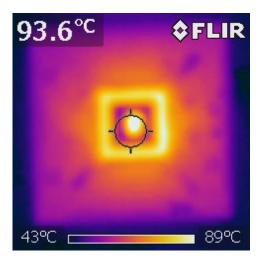

| 2.3  | SLIDER4 ASIC photos taken with a thermal imager                                | 38  |

|      | a SLIDER4 ASIC temperature during tests at room temperature                    | 38  |

|      | b SLIDER4 ASIC temperature during tests at $-40^{\circ}C$                      | 38  |

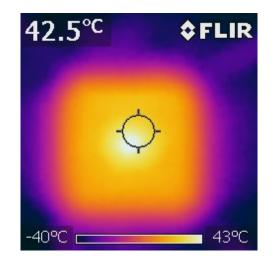

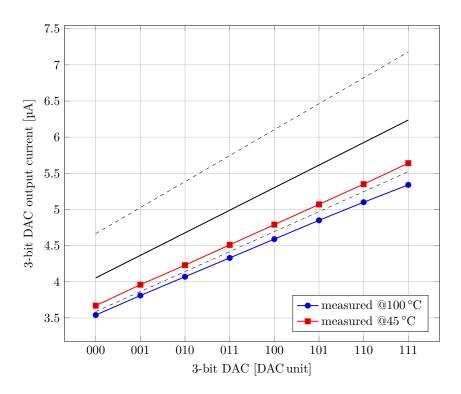

| 2.4  | 3-bit DAC currents as a function of the DAC unit. The black line represents    |     |

|      | the typical case at room temperature. The lower dashed line represents         |     |

|      | the SS case whereas the higher dashed line represents and FF case at room      |     |

|      | temperature.                                                                   | 39  |

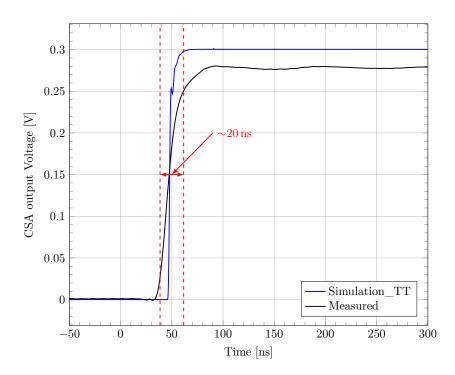

| 2.5  | channel 3 CSA output, in the time domain. The rise time is highlighted         | 41  |

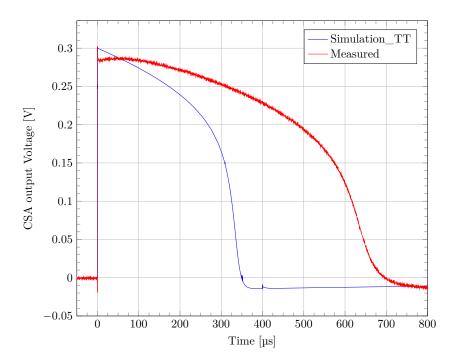

| 2.6  | channel 3 CSA output, in the time domain.                                      | 42  |

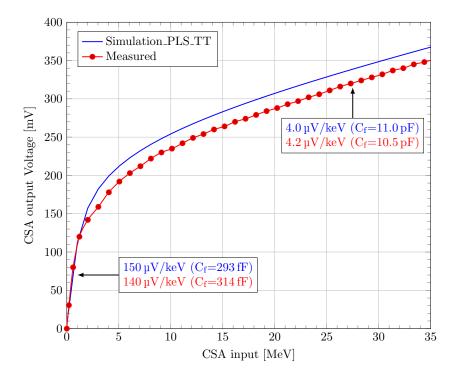

| 2.7  | channel 3 input-output characteristic for an injected charge corresponding     |     |

|      | to an energy range from 20 keV to 35 MeV                                       | 43  |

|      |                                                                                |     |

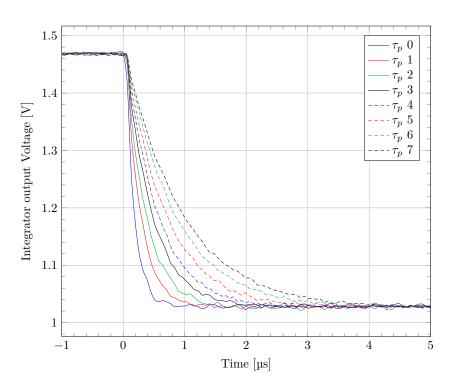

| 2.8  | channel 3 integrator output, in the time domain.                            | 43 |

|------|-----------------------------------------------------------------------------|----|

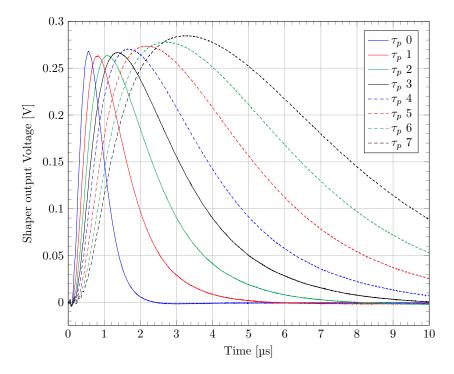

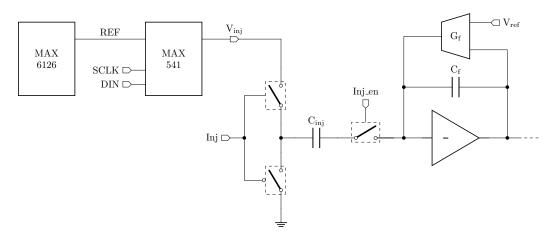

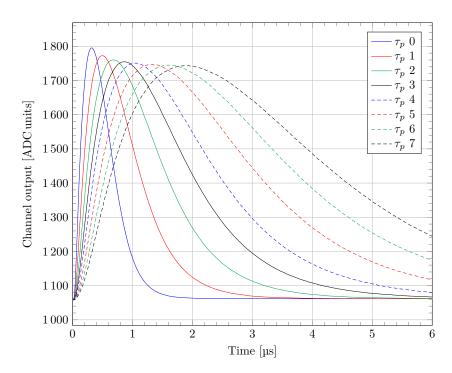

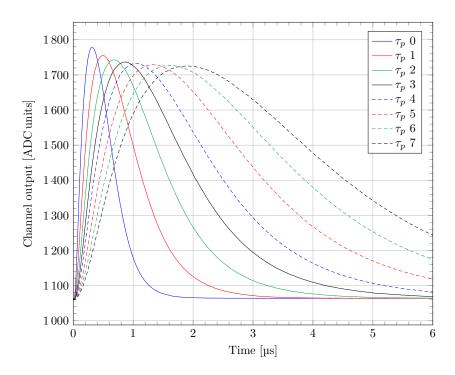

| 2.9  | channel 3 shaper output for all peaking times.                              | 44 |

| 2.10 | channel 3 differentiator output for peaking times from 1 to 7               | 45 |

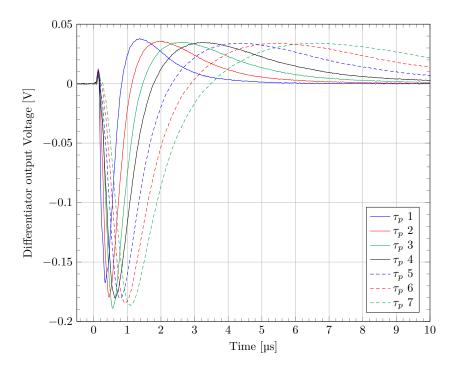

| 2.11 | channel 3 ENE as a function of the peaking time                             | 46 |

| 2.12 | injection circuit used to test the GAPS front-end channel                   | 47 |

| 2.13 | SLIDER8 read event data packet.                                             | 50 |

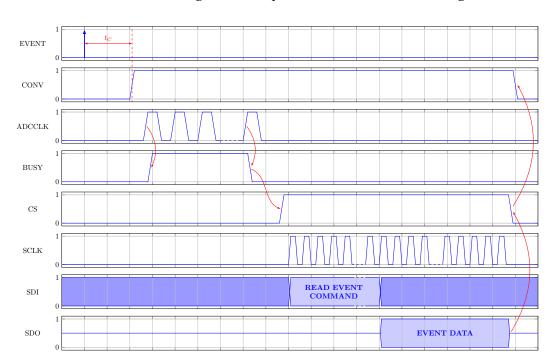

| 2.14 | SLIDER8 non-self-trigger injection and read procedure.                      | 51 |

| 2.15 | SLIDER8 self-trigger injection and read procedure.                          | 53 |

| 2.16 | SLIDER8 Channel output for channel 1. The injected charge corresponds       |    |

|      | to an energy signal of 15.43 MeV.                                           | 54 |

| 2.17 | SLIDER8 Channel output for channel 8. The injected charge corresponds       |    |

|      | to an energy signal of 15.43 MeV.                                           | 55 |

| 2.18 | SLIDER8 channel output for channel 5 and peaking time 6 as obtained by      |    |

|      | varying the calibration voltage                                             | 56 |

| 2.19 | SLIDER8 input-output trans-characteristics for channel 6 at all the se-     |    |

|      | lectable peaking times. The injected charge varies from 0 to 30000 DAC      |    |

|      | units (1.018 pC, 23.15 MeV)                                                 | 57 |

| 2.20 | SLIDER8 input-output trans-characteristics for all the channels and peaking |    |

|      | time 7. The injected charge varies from 0 to 30000 DAC units (1.018 pC,     |    |

|      | 23.15 MeV)                                                                  | 58 |

| 2.21 | SLIDER8 low energy gain for channel 5 at all the selectable peaking times.  | 58 |

| 2.22 | SLIDER8 threshold scan of the channel 4 as obtained by varying the peaking  |    |

|      | time                                                                        | 60 |

| 2.23 | SLIDER8 threshold scan for all the channels and peaking time 3              | 61 |

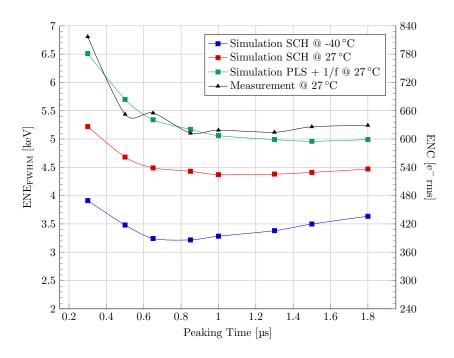

| 2.24 | mean SLIDER8 ENE                                                            | 63 |

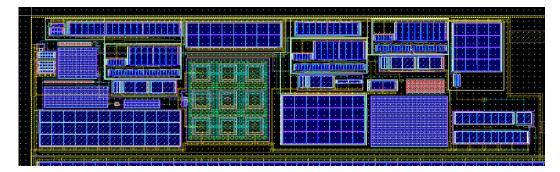

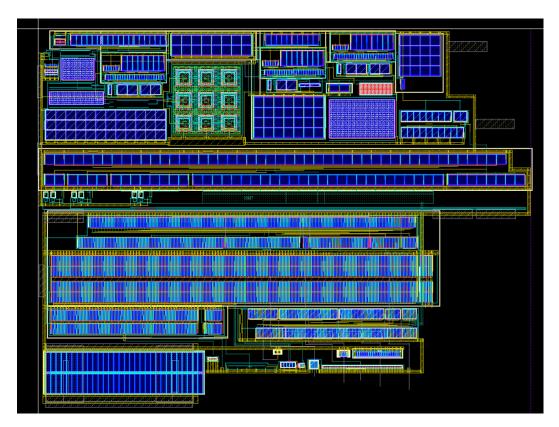

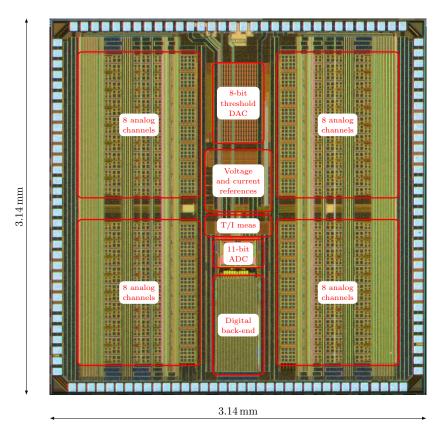

| 3.1  | pSLIDER32 layout                                                            | 65 |

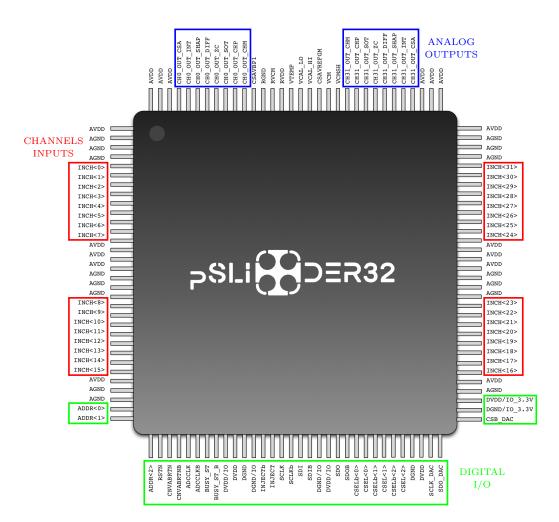

| 3.2  | pSLIDER32 pin diagram.                                                      | 67 |

| 3.3  | pSLIDER32 package                                                           | 68 |

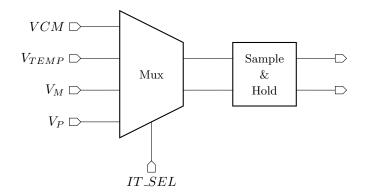

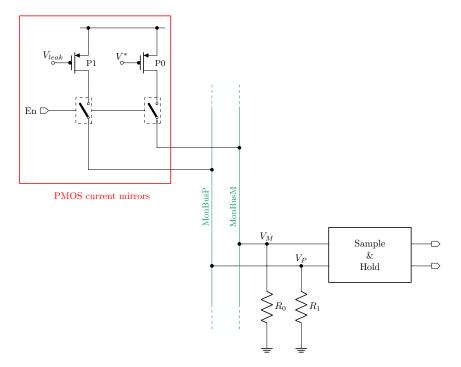

| 3.4  | pSLIDER32 Multiplexer                                                       | 68 |

| 3.5  | pSLIDER32 Leakage Current Detector.                                         | 70 |

| 3.6  | pSLIDER32 read temperature sensor/leakage current packet.                   | 73 |

| 3.7  | analog switches schematic of the pSLIDER32 test board. This structure is    |    |

|      | replicated on the test board for channels 0 and 31                          | 75 |

| 3.8  | pSLIDER32 front-end board.                                                  | 76 |

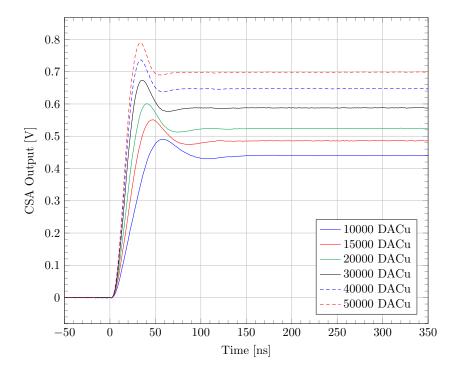

| 3.9  | pSLIDER32 CSA output of the channel 0. The amplitude has a gain factor      |    |

|      | of 2 introduced by a non-inverting operational amplifer used to decouple    |    |

|      | the CSA output from the oscilloscope probe.                                 | 78 |

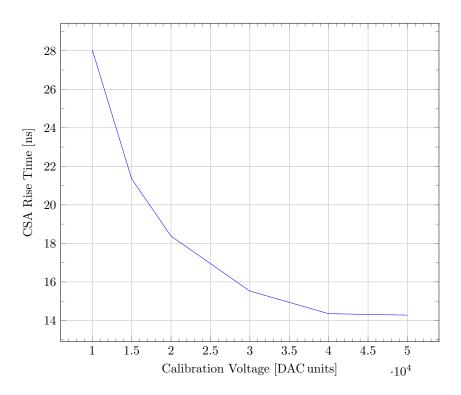

| 3.10 | pSLIDER32 CSA rise times of the channel 0 as a function of the injected     |    |

|      | charge                                                                      | 78 |

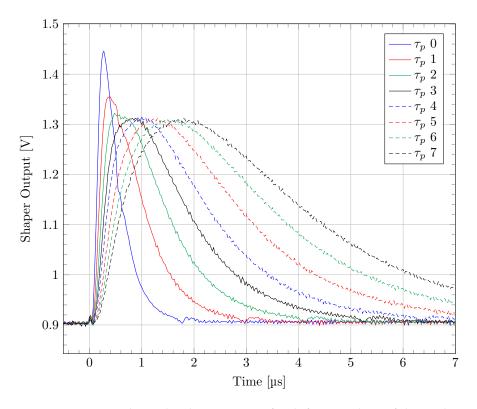

| 3.11 | pSLIDER32 channel 0 shaper output for different values of the peaking time. | 79 |

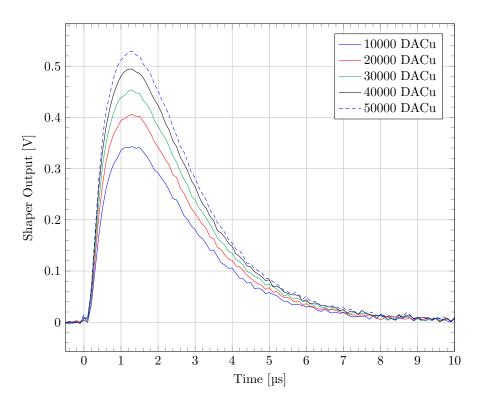

| 3.12 | pSLIDER32 channel 0 shaper output for different values of the injected      |    |

|      | charge and for the peaking time 5                                           | 80 |

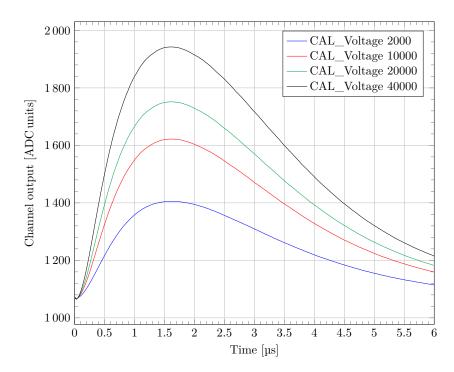

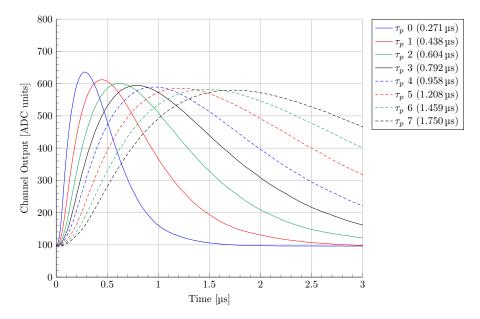

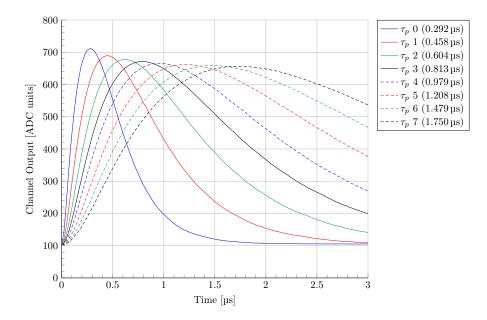

| 3.13 | pSLIDER32 channel 0 output as obtained by varying the peaking time          | 81 |

|      | pSLIDER32 channel 28 output as obtained by varying the peaking time         | 82 |

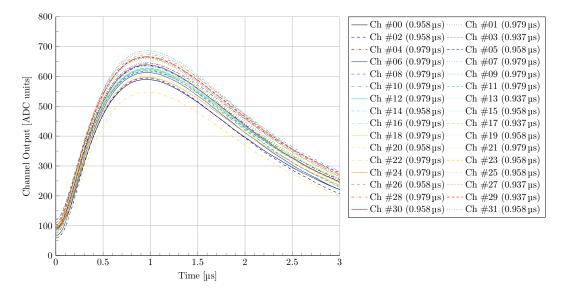

| 3.15 | pSLIDER32 all channels output for peaking time 4                            | 83 |

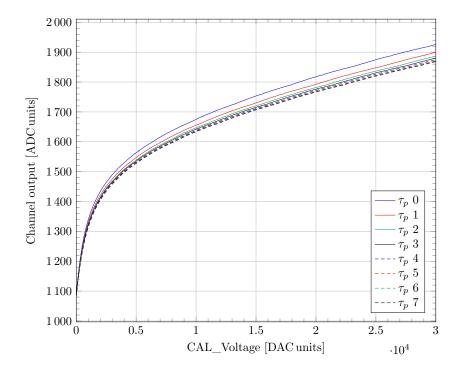

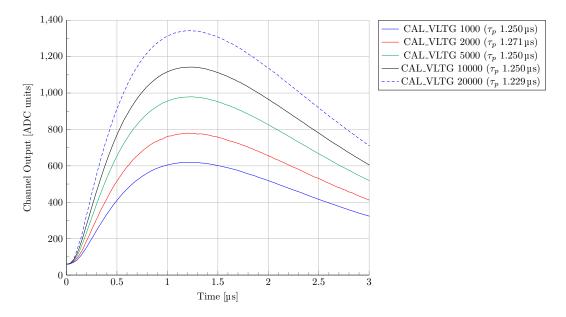

| 3.16 | pSLIDER32 channel 15 output for peaking time 5 as obtained by varying                                                                                                                                                                                                                                      |       |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      | the calibration voltage.                                                                                                                                                                                                                                                                                   | . 84  |

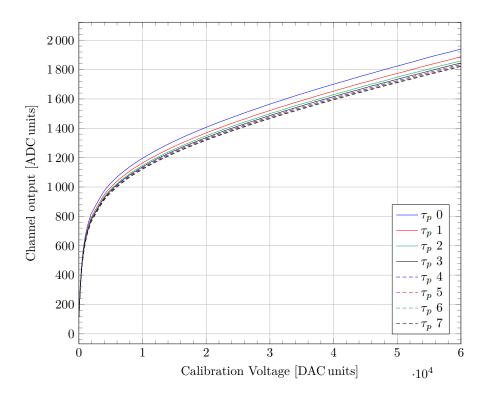

| 3.17 | input-output trans-characteristic for pSLIDER32 channel 12 measured for all the selectable peaking times.                                                                                                                                                                                                  | . 84  |

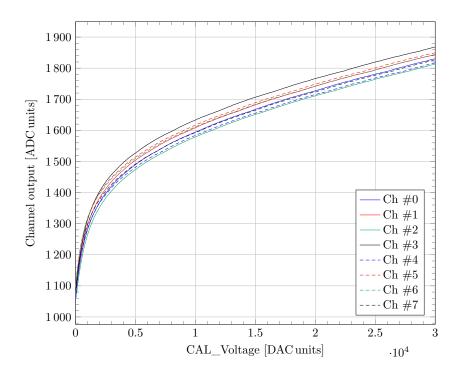

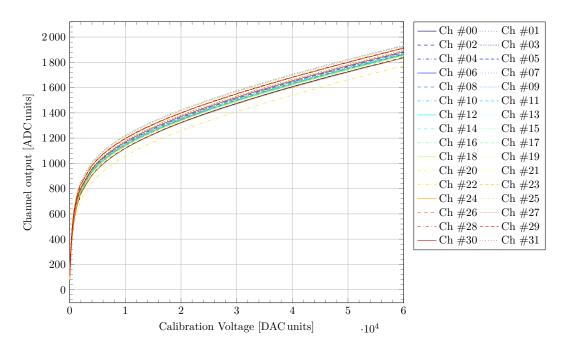

| 3.18 | input-output trans-characteristic for all the channels in the pSLIDER32 chip (peaking time 2).                                                                                                                                                                                                             | . 85  |

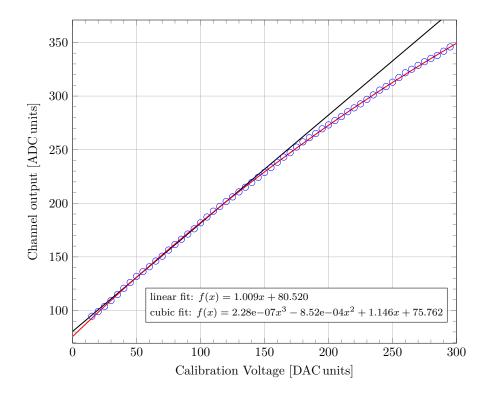

| 3.19 | input-output trans-characteristic for channel 11 in the high gain region (peaking time 3)                                                                                                                                                                                                                  | . 86  |

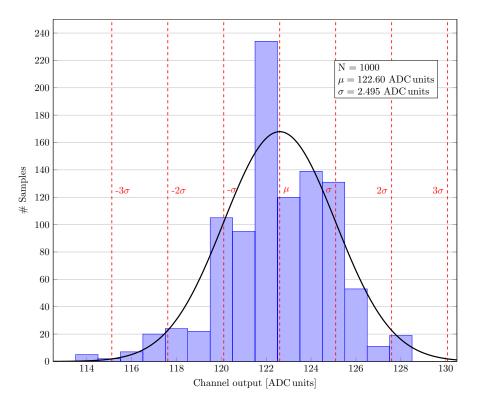

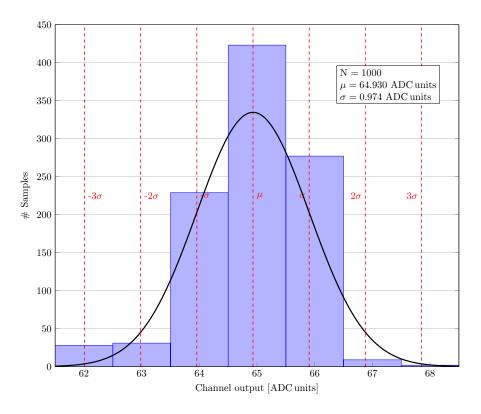

| 3.20 | pSLIDER32 channel 8 pedestal for peaking time 0                                                                                                                                                                                                                                                            |       |

|      | pSLIDER32 channel 21 pedestal for peaking time 6.                                                                                                                                                                                                                                                          |       |

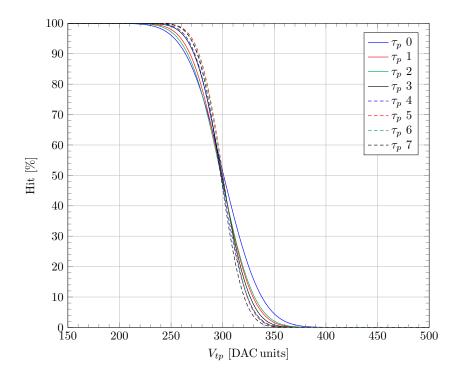

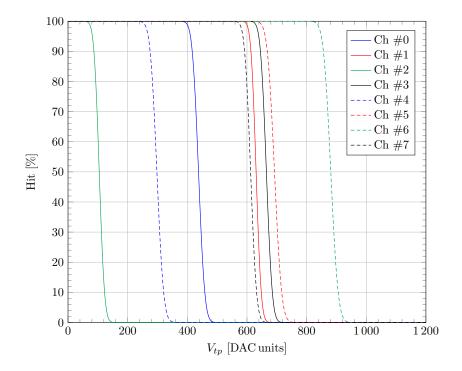

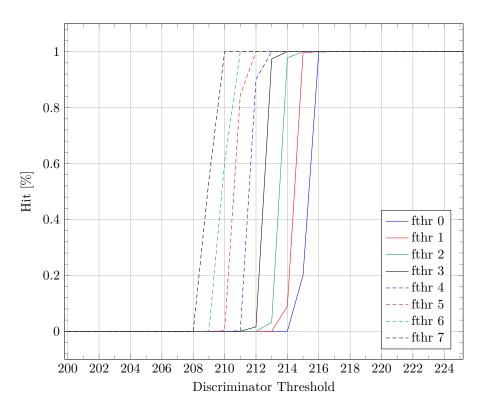

|      | pSLIDER32 channel 18 threshold scan for the peaking time 5 as obtained<br>by varying the fine threshold.                                                                                                                                                                                                   | . 88  |

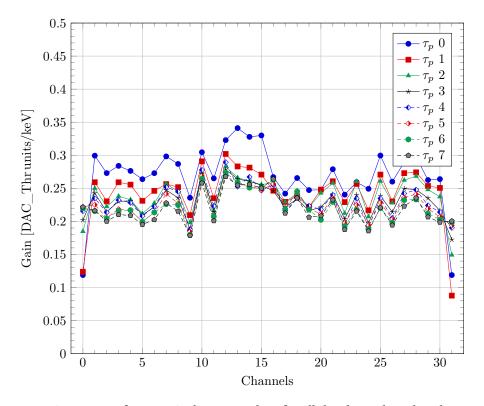

| 3.23 | Conversion from DAC_thr units to keV for all the channels and peaking times.                                                                                                                                                                                                                               | . 89  |

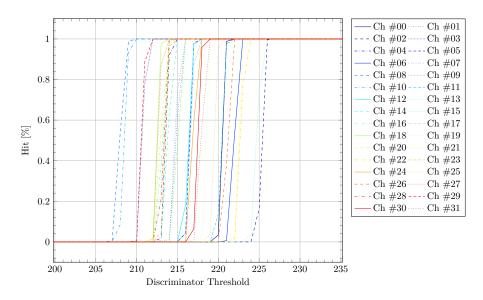

| 3.24 | threshold scan for all the channels in pSLIDER32 for the peaking time 4 with the fine threshold set to 011.                                                                                                                                                                                                | . 90  |

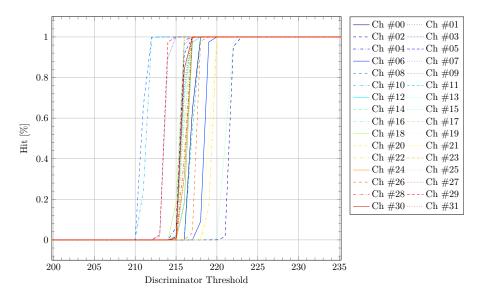

| 3.25 | threshold scan for all the channels in pSLIDER32 for the peaking time 4                                                                                                                                                                                                                                    |       |

|      | with the fine threshold set to minimize the threshold dispersion                                                                                                                                                                                                                                           | . 91  |

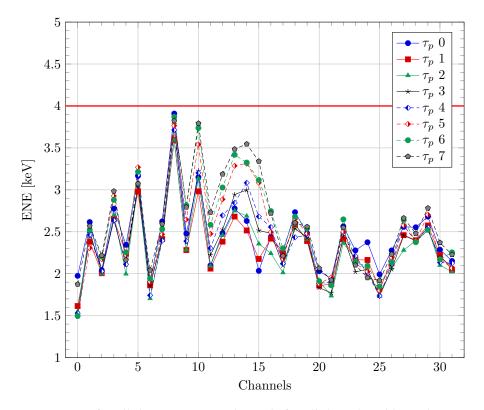

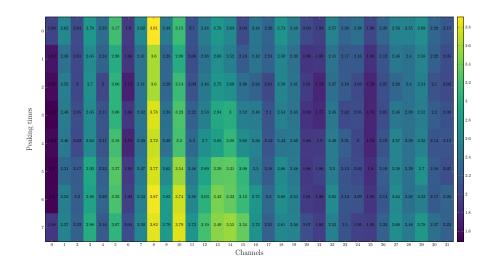

| 3.26 | ENE for all the pSLIDER32 channels for all the selectable peaking times.                                                                                                                                                                                                                                   |       |

| 3.27 |                                                                                                                                                                                                                                                                                                            |       |

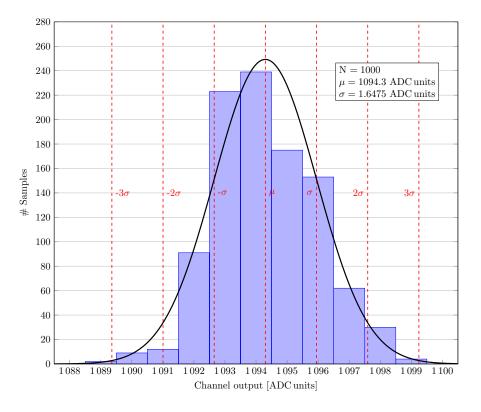

| 3.28 | statistical analysis of pSLIDER32 channel 21 output sampled 1000 times in                                                                                                                                                                                                                                  | • • - |

|      | self-trigger mode for peaking time 4                                                                                                                                                                                                                                                                       | . 93  |

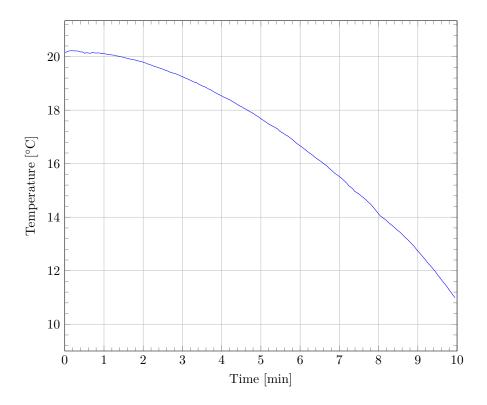

| 3.29 | tions from 20 °C to 10 °C                                                                                                                                                                                                                                                                                  | . 95  |

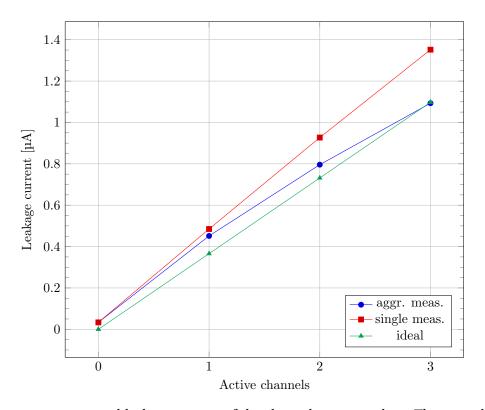

| 3.30 | aggregated leakage current of the channels 15, 16 and 17. The green line<br>corresponds to the expected value of the detected current. The blue line<br>corresponds to the acquired value with more active channels. The red line<br>corresponds to the sum of the currents acquired with only one channel |       |

|      | active for each acquisition.                                                                                                                                                                                                                                                                               | . 97  |

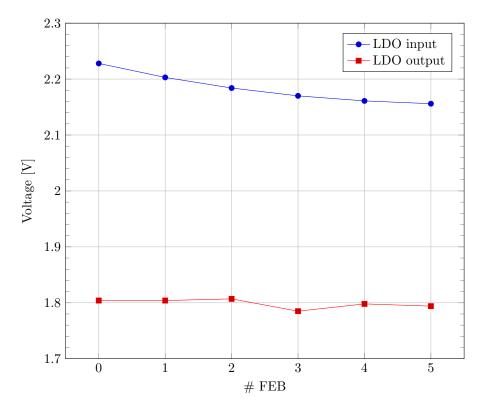

| 3.31 | LDO inputs and outputs for all the 6 modules connected in series                                                                                                                                                                                                                                           | . 98  |

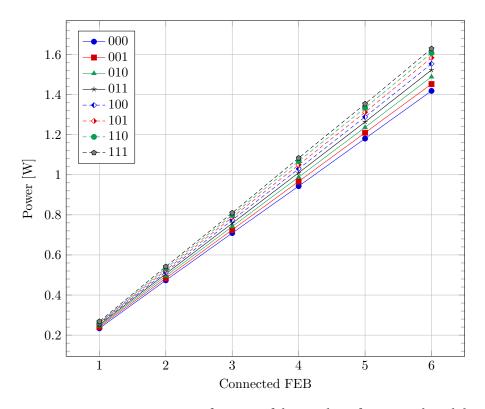

| 3.32 | current consumption as a function of the number of connected modules and for all the bias register codes combinations.                                                                                                                                                                                     | . 99  |

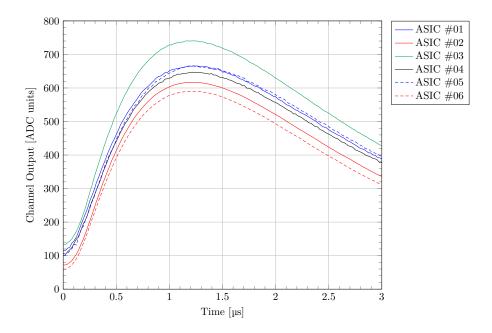

| 3.33 | pSLIDER32 waveform scan for the channel 2 and peaking time 5 for all the 6 ASICs connected in series.                                                                                                                                                                                                      | . 100 |

| 3.34 | input-output channel trans-characteristics, obtained from digital measurements, for channel 20 and peaking time 5 for all the 6 modules connected                                                                                                                                                          |       |

|      | in series.                                                                                                                                                                                                                                                                                                 |       |

|      | entire final GAPS tracking system.                                                                                                                                                                                                                                                                         | . 108 |

| A.36 | two front-end boards, with a mounted ASIC, connected via one flex-rigid                                                                                                                                                                                                                                    |       |

| D    | board.                                                                                                                                                                                                                                                                                                     |       |

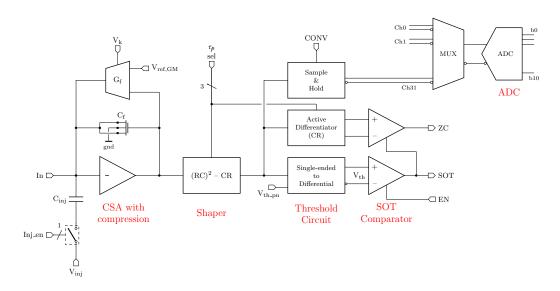

|      | front-end channel schematic.                                                                                                                                                                                                                                                                               | . 110 |

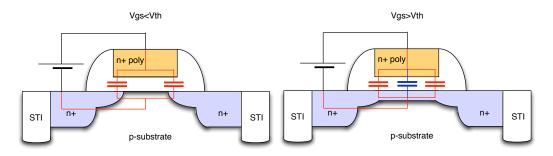

| B.38 | nMOS capacitance variation. In the left image $(V_{gs} < V_{nMOS,th})$ only the <i>overlap</i> capacitors compose the nMOS capacitance. In the right image                                                                                                                                                 |       |

|      | $(V_{gs} < V_{nMOS,th})$ the nMOS capacitance is composed of the sum of the                                                                                                                                                                                                                                |       |

|      | overlap and the channel capacitors.                                                                                                                                                                                                                                                                        | . 111 |

#### LIST OF FIGURES

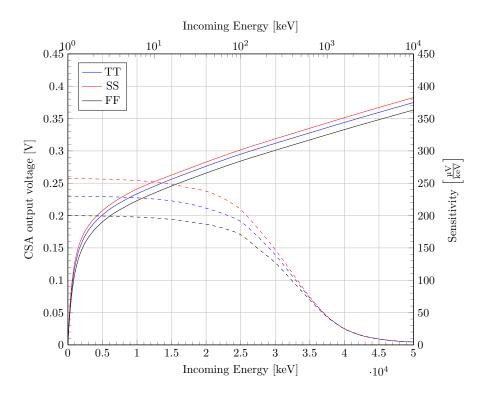

- B.39 the continuous lines represent the CSA output as a function of the charge injected (x-axis on the lower part of the image, y-axis on the left part). The dashed lines represent the CSA output sensitivity function of the incoming energy (x-axis on the upper part of the image, y-axis on the right part). . . 112

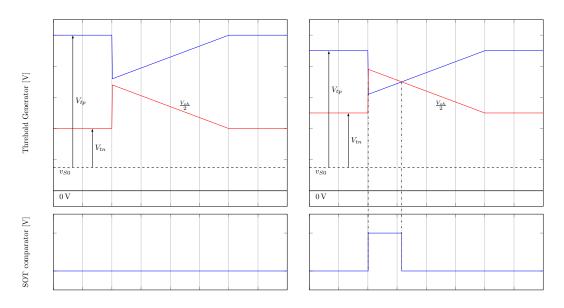

- B.40 examples of threshold generator and SOT comparator outputs as obtained by varying the threshold voltages  $V_{tp}$  and  $V_{tn}$ . In the diagrams on the left, the SOT comparator does not fire since  $V_{sh} < (V_{tp} - Vtn)$ . Otherwise in the diagrams on the right, the SOT comparator is at logic 1 when  $V_{sh} > (V_{tp} - Vtn)$ . 114

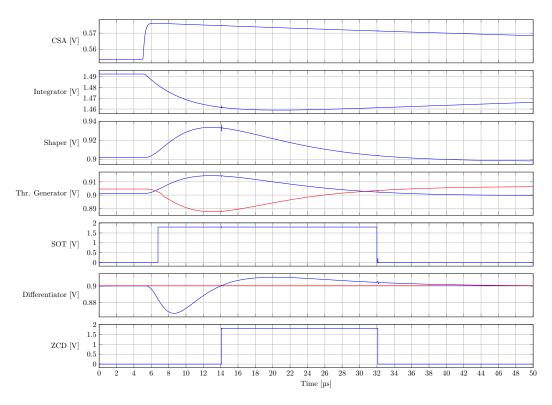

- B.41 all channel blocks signals for an incoming energy of 100 keV at  $-40~^\circ\text{C.}$  . . 115

# List of Tables

| 1.1  | Bandgap process and mismatch Monte Carlo simulations                                                 | 8  |

|------|------------------------------------------------------------------------------------------------------|----|

| 1.2  | phase margin of OP1 and OP2 feedback loop                                                            | 13 |

| 1.3  | Values of current $I_{mir}$ by varying: supply voltage, temperature and process                      |    |

|      | parameters                                                                                           | 15 |

| 1.4  | Process and mismatch Monte Carlo simulations.                                                        | 15 |

| 1.5  | Values of current $I_{DAC}$ by varying: DAC combinations, temperature and                            |    |

|      | process parameters.                                                                                  | 20 |

| 1.6  | Currents needed by GAPS Front-end IP blocks                                                          | 21 |

| 1.7  | current values obtained by using the current generator, its 3-bit DAC and                            |    |

|      | the current mirrors deigned for the GAPS channel. In TT, FS, and SF cases                            |    |

|      | the 3-bit DAC has been set to 011. In FF case it has been set to 001. In SS                          |    |

|      | case the 3-bit DAC has been set to 101.                                                              | 23 |

| 1.8  | mismatch Monte Carlo simulations (1000 iterations) of the current values                             |    |

|      | mirrored in each GAPS analog block.                                                                  | 24 |

| 1.9  | process and mismatch Monte Carlo simulations.                                                        | 24 |

| 1.10 | 4-bit binary-to-thermometer decoder input and output                                                 | 27 |

| 2.1  | measured and simulated Bandgap voltage output (BG_V $_{\rm out})$ and current                        |    |

|      | generator output (BG_ $i_{out}$ ). The temperature in brackets is the ambient                        |    |

|      | temperature, the other is the measured chip temperature. Simulations                                 |    |

|      | refers to measured chip temperature.                                                                 | 40 |

| 2.2  | comparison between measured and simulated peaking times for the signal at the SLIDER4 shaper output. | 44 |

| 2.3  | comparison between measured peaking times of the SLIDER4 shaper and                                  |    |

|      | the Zero-Crossing time of the SLIDER4 differentiator.                                                | 45 |

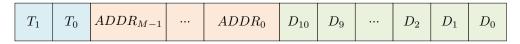

| 2.4  | reading and writing messages format of SLIDER8 digital back-end                                      | 49 |

| 2.5  | Structure of the first 2 bits of the Read Event Data Packet                                          | 50 |

| 2.6  | Comparison between ideal $\tau_p$ and measured $\tau_p$ .                                            | 55 |

| 2.7  | measured $\tau_3$ and $\tau_5$ for different values of the injected charge.                          | 56 |

| 2.8  | SLIDER8 low energy region gain for all the selectable peaking times                                  | 59 |

| 2.9  | fit values obtained by fitting the data values for channel 4                                         | 59 |

| 2.10 | fit values obtained with peaking time 3                                                              | 60 |

| 3.1  | Reading and writing messages format of pSLIDER32 digital back-end                                    | 73 |

| 3.2  | pSLIDER32 SEU flags.                                                                                 | 74 |

| 3.3  | pSLIDER32 measured peaking times, obtained from analog measurements,                                 |    |

|      | for the peaking time 5 and different values of the injected charge                                   | 79 |

| 3.4  | pSLIDER32 peaking times obtained from digital measurements                                           | 82 |

| 3.5  | pSLIDER32 baseline values. All the values are expressed in <i>ADC units</i>                          | 82 |

## LIST OF TABLES

| 3.6  | pSLIDER32 high gain values obtained with the linear regression and the          |     |

|------|---------------------------------------------------------------------------------|-----|

|      | cubic regression. All the values are expressed in $\frac{ADC units}{DAC units}$ | 86  |

| 3.7  | statistical analysis (mean and standard deviation) of channel output, sam-      |     |

|      | pled 1000 times in self-trigger mode, for all the channels and for the peaking  |     |

|      | time 4                                                                          | 94  |

| 3.8  | detected leakage current for pSLIDER32 channels 15,16 and 17 . Resistors        |     |

|      | of 8.2 M  have been used in order to generate these currents                    | 96  |

| 3.9  | aggregated detected leakage current for channels 15, 16 and 17.                 | 96  |

| 3.10 | pSLIDER32 measured peaking times, obtained from digital measurements,           |     |

|      | for the channel 2 and peaking time 5 for all the 6 modules connected in         |     |

|      | series                                                                          | 100 |

| B.11 | GAPS ASIC requirements.                                                         | 110 |

## Introduction

One of the towering problems of early 21th century physics is the identification and discovery of the nature of dark matter which, according to different studies, is expected to account for about the 86% of the universe mass. The dark matter is an hypothetical component of matter not directly observable, because, with respect to the known matter, it does not emit electromagnetic radiation and it manifests itself only by gravitational effects. The existence of non-relativistic particles, which weakly interact with the known matter by gravitational force and weak nuclear force, has been hypothesized: they are called WIMPs (Weakly Interacting Massive Particles).

In this scope, the GAPS (General AntiParticle Spectometer) experiment arises as a modern approach to the indirect search of the dark matter, leading to a complementary type of research. In fact, GAPS aim is not to directly detect the WIMPs, but, instead, the anti-deuteron that is produced by the WIMPs auto-annihilations. Cosmic rays rarely produce anti-deuteron particles with energies below 0.25 GeV whereas the dark matter models predict a higher number of anti-deuterons produced even at these low energies. In the physics experiments, the anti-deuteron was never revealed, so its non-ambiguous detection will be very significant. In physics theories, anti-deuteron would be produced in high concentration zones of dark matter with a high rate of annihilations. The antiparticles produced by the dark matter are captured by a target material with the consequent formation of an exotic excited atom. This exotic atom quickly decays, producing X-rays at uniquely defined energies and after the subsequent nuclear annihilation, other particles as pions and protons. The GAPS detection method consists of a Time-Of-Flight (TOF) system, for a first selection of the particles of interest, and a solid state tracker based on Lithium-Drifted Silicon (Si(Li)) detectors, which reconstruct the particle traces and velocities. From this data it is possible to obtain information about the particle energy and its type. The research project discussed in this thesis work is focused on the design of the front-end electronics for the GAPS Si(Li) tracker.

The thesis work is organized as follows. In the Chapter 1 the design of three IP blocks for the detector readout channel is described. The first designed IP block is a bandgap voltage reference. This block's main task is to generate a PVT (P: manufacturing process variations, V: supply voltage, T: temperature) independent, stable voltage which will be used in other channel blocks. In particular, the generated voltage is used by the second IP block: a current generator. This generates a fixed current of 5  $\mu$ A, made process independent by the design of a specific 3-bit DAC, included in the current generator design. The currents are then mirrored in other branches of the channel with a gain factor dependent on the required current. The last designed IP block is an 8-bit DAC used to generate two threshold voltages needed by a channel comparator.

The Chapter 2 is focused on the characterization of the two first designed ASIC prototypes: SiLI DEtector Readout 4 (SLIDER4) and SiLI DEtector Readout 8 (SLIDER8). SLIDER4 is a 4-channels simplified version of the final ASIC which has been used to validate the functionality of all the main blocks included in the readout channel. SLIDER8 is a simplified

#### LIST OF TABLES

version of the final ASIC, too. Beside 8 analog readout channels it also includes an 11-bit SAR ADC and a digital back-end section.

In Chapter 3 the results obtained from the characterization of the first prototype of the flight ASIC, pSLIDER32, are described. The ASIC has been tested as a standalone device and also once mounted on the front-end board designed for the final experiment. Moreover, since the assembly of the tracker requires the connection of 6 front-end boards in a chain, 6 front-end boards (with the mounted ASIC) connected with each other have been tested. Measurement results of this chain executed with pSLIDER32 ASICs are reported in this chapter, too.

All ASICs need IP blocks to work properly. In particular three IP blocks, needed by the GAPS ASIC, will be described in this chapter: a bandgap voltage reference, which generates a PVT (P: manufacturing process variations, V: supply voltage, T: temperature) independent, stable voltage, a current generator (and a 3-bit DAC for its fine trimming) used to bias all the blocks of the analog readout channel of the GAPS ASIC by means of current mirrors, and a 8-bit DAC used to generate two threshold voltages needed by the readout channel comparator.

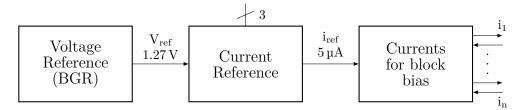

## 1.1 Voltage and current reference

The analog front-end channel designed for the readout of the Si(Li) detector of the GAPS experiment (appendix A) is comprised of several blocks, as discussed in detail in appendix B. Each element of the channel requires one or more current references to be properly biased. These references should remain constant regardless of the external conditions like temperature, variations in the ASIC supply voltage and process parameter mismatch in fabrication. To comply with this requirement, a solution where the reference currents are generated starting from a precise voltage reference has been adopted, as shown in fig. 1.1. Starting from this voltage (Voltage Reference: BGR), a 3-bit adjustable current can be obtained and then the final reference currents can be derived. Each of these blocks will be discussed in detail in this section.

Figure 1.1: block diagram of GAPS voltage and current references.

### 1.1.1 Bandgap Voltage Reference

A voltage reference is an essential block in the design of any integrated circuit. The goal of a bandgap voltage reference is to generate a PVT independent stable voltage. In order to achieve this goal, the following basic principle is usually adopted, i.e. the reference voltage is obtained as the sum of two voltages [1]:

•  $V_1$  with positive temperature coefficient (TC),  $\frac{\partial V_1}{\partial T} = k_1$ , where  $k_1 > 0$ ;

•  $V_2$  with negative temperature coefficient (NC),  $\frac{\partial V_2}{\partial T} = k_2$ , where  $k_2 < 0$ .

Moreover, the derivative of the sum of these two voltages, with respect to the temperature, must be equal to 0:

$$\frac{\partial V_{out}}{\partial T} = \frac{\partial V_1}{\partial T} + \frac{\partial V_2}{\partial T} = k_1 + k_2 = 0.$$

(1.1)

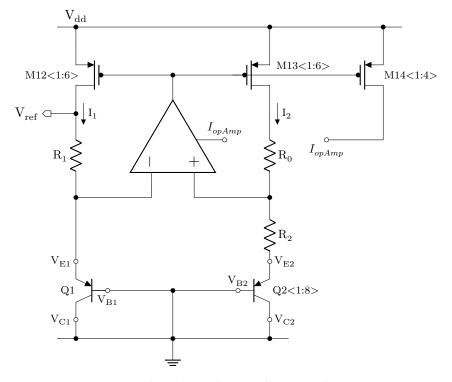

The schematic of the bandgap designed for the the GAPS current generator, is one of the most widely used in commercial applications and is depicted in fig. 1.2 [2]. Because of the negative feedback network of the operational amplifier, the voltage at its non-inverting input,  $V^-$ , is equal to the voltage at its inverting input,  $V^+$ . PMOS M12, M13 and M14 are in current mirror configuration. The current which flows in the drain terminal of a PMOS operating in saturation mode can be defined as [3]:

$$I_D = \frac{1}{2} \mu_p C_{ox} \cdot \left(\frac{W}{L}\right) \cdot \left(V_{SG} - \left|V_{tp}\right|\right)^2 \cdot \left(1 + \left|\lambda\right| V_{SD}\right)$$

(1.2)

where  $\lambda$  is a device parameter whose units are reciprocal volts  $[V^{-1}]$ ,  $C_{ox}$  is the gate oxide capacitance per unit area  $[F/m^2]$ ,  $\mu_p$  is the charge-carrier effective mobility while W and L are respectively the width and length of the MOS channel. PMOS M12 and M13 have the same dimensions, so  $V_{tp,M12} = V_{tp,M13}$ ,  $W_{M12} = W_{M13}$ ,  $L_{M12} = L_{M13}$  and  $\lambda_{M12} = \lambda_{M13}$ . Moreover, by design, they have the same  $V_{SG}$ . Resistors  $R_0 = R_1$  are inserted to guarantee  $V_{SD,M12} = V_{SD,M13}$ , suppressing current mismatch due to channel-length modulation. PMOS M14 is used to provide the bias current to the operational amplifier described in detail in section 1.1.2. After all these considerations, the two currents  $I_1$  and  $I_2$  can be considered as equal ( $I_1 = I_2$ ). The constant voltage  $V_{ref}$  can be extracted from the following equivalence:

$$\frac{V_{ref} - V^-}{R_1} = \frac{V^+ - V_{E2}}{R_2},\tag{1.3}$$

where  $V^- = V^+ = V_{EB1}$  and  $V_{E2} = V_{EB2}$ . So:

$$V_{ref} = V_{EB1} + \frac{R_1}{R_2} \cdot (V_{EB1} - V_{EB2}) = V_{EB1} + \frac{R_1}{R_2} \cdot \Delta V_{EB}.$$

(1.4)

By differentiating  $V_{ref}$  with respect to the absolute temperature we obtain two terms: one proportional to the absolute temperature (PTAT) the other proportional to the complementary absolute temperature (CTAT), as shown in the following equation:

$$\frac{\partial V_{ref}}{\partial T} = \frac{\partial V_{EB1}}{\partial T} + \frac{\partial \Delta V_{EB}}{\partial T} \cdot \frac{R_1}{R_2}.$$

(1.5)

#### **Negative TC voltage**

The pnp BJT consists of three semiconductor regions: the emitter region E (p-type), the base region B (n-type) and the collector region C (p-type). These regions form two pn junctions, the emitter-base junction (EBJ) and the collector-base junction (CBJ). In this project, the pnp has been used as a diode-connected transistor, namely  $V_E > V_B$  (forward biased EBJ junction) and  $V_B = V_C$  (reverse biased CBJ junction). A characteristic of diode-connected

Figure 1.2: bandgap voltage reference schematic.

BJTs is that they are always in the forward active region. The emitter current of a pnp in diode-connected configuration can be defined using the Shockley diode equation [3]:

$$I_E = I_S \left[ \exp\left(\frac{V_{EB}}{V_T}\right) - 1 \right], \tag{1.6}$$

where  $V_T = (k_B \cdot T) / q$  is the thermal voltage,  $k_B$  is the Boltzmann constant, T is the absolute temperature, q is the elementary charge and  $I_S$  is the saturation current (which is an intrinsic transistor parameter). Even for small  $V_{EB}$ , the exponential is very large, since the thermal voltage is very small in comparison (at 300 K,  $V_T = 25.85$  mV), so that the diode equation can be approximated by [3]:

$$I_E \approx I_S \cdot \exp\left(\frac{V_{EB}}{V_{\rm T}}\right).$$

(1.7)

The saturation current of a BJT, can be defined as [3]:

$$I_S = \frac{A_{\varepsilon} q D_p p_{n0}}{W} \tag{1.8}$$

where  $p_{n0}$  is the thermal-equilibrium value of the minority-carrier (hole) concentration in the base region,  $A_{\varepsilon}$  is the cross-sectional area of the base-emitter junction,  $D_p$  is the hole diffusion coefficient in the base, W is the effective width of the base. By expressing  $p_{n0} = p_i^2/N_A$ , where  $p_i$  is the intrinsic carrier density and  $N_A$  is the doping concentration in the base,  $I_S$  can be expressed as [3]:

$$I_S = \frac{A_{\varepsilon} q D_p p_i^2}{N_A W} \tag{1.9}$$

Typically  $I_S$  is in the range from  $10^{-12}$  A to  $10^{-18}$  A and is a strong function of temperature, approximately doubling every 5 °C rise in temperature. In fact:

- $p_i = BT^{3/2} \exp(-E_g/2k_BT)$ . *B* is a material-dependent parameter that is  $7.3 \cdot 10^{15} \text{ cm}^{-3}\text{K}^{-3/2}$  for silicon [3].

- $E_g$  is the bandgap energy of silicon. The relationship between band gap energy and temperature can be described by Varshni's empirical expression [4]:

$$E_g(T) = E_g(0) - \frac{\alpha T^2}{T + \beta}.$$

(1.10)

In silicon:  $\alpha = 4.73 \cdot 10^{-4} \text{ eV/K}$ ,  $\beta = 636 \text{ K}$  and  $E_g(0) = 1.17 \text{ eV}$  [5]. In the range of temperature of interest (from  $-40 \text{ }^{\circ}\text{C}$  up to  $30 \text{ }^{\circ}\text{C}$ ) the bandgap energy of silicon can be considered constant, and its value is 1.14 eV. So, from here on,  $E_g = 1.14 \text{ eV}$  will be considered.

- $D_p = \mu_p V_T$ . This is the electrical mobility equation coming from the Einstein Smoluchowski diffusion relation, where  $\mu_p$  is the hole mobility in silicon.

- Regarding the temperature dependence of  $\mu_p$  in silicon, the function  $\mu_p(T)$  is often approximated as

$$\mu_p(T) = \mu_{p0} \left(\frac{T}{300 \,\mathrm{K}}\right)^m. \tag{1.11}$$

where  $\mu_{p0} = 470.5 \text{ cm}^2/(\text{V} \cdot \text{s})$  (it is the maximum mobility, with no doping) and m = -2.2 [6, 7].

From these equations, it can be found that  $I_S$  is proportional to  $\mu_p k_B T p_i^2$  [1]. Thus,

$$I_S = b \cdot T^{4+m} \cdot \exp\left(\frac{-E_g}{kT}\right) \tag{1.12}$$

where *b* is a proportionality factor, which contains all the temperature independent terms. Writing  $V_{EB} = V_T \cdot \ln (I_E/I_s)$ , the TC of the base-emitter voltage can be computed. Given the derivative of  $V_{EB}$  with respect to T, the behavior of  $I_E$  as a function of the temperature is known. To simplify the analysis, the current  $I_E$  is held constant. Thus,

$$\frac{\partial V_{EB}}{\partial T} = \frac{\partial V_T}{\partial T} \cdot \ln \frac{I_E}{I_S} - \frac{V_T}{I_S} \cdot \frac{\partial I_S}{\partial T}.$$

(1.13)

From eq. (1.12):

$$\frac{\partial I_S}{\partial T} = b \cdot (4+m) \cdot T^{3+m} \cdot \exp\left(\frac{-E_g}{kT}\right) + b \cdot T^{4+m} \cdot \exp\left(\frac{-E_g}{kT}\right) \cdot \frac{E_g}{kT^2}.$$

(1.14)

Therefore,

$$\frac{V_T}{I_S}\frac{\partial I_S}{\partial T} = (4+m)\frac{V_T}{T} + \frac{E_g}{kT^2} \cdot V_T.$$

(1.15)

By combining eq. (1.13) and eq. (1.15) [1]:

$$\frac{\partial V_{EB}}{\partial T} = \frac{V_T}{T} \ln \frac{I_C}{I_S} - (4+m) \frac{V_T}{T} - \frac{E_g}{kT^2} \cdot V_T$$

(1.16)

$$=\frac{V_{EB} - (4+m) \cdot V_T - E_g/q}{T}$$

(1.17)

The eq. (1.17) gives the temperature coefficient of the base-emitter voltage at a given temperature T, revealing dependence on the magnitude of  $V_{EB}$  itself. With  $V_{EB} \approx 780 \text{ mV}$  and T = 233 K,  $\partial V_{EB}/\partial T = -1.7 \text{ mV/K}$ . From the eq. (1.17), it can be noted that the temperature coefficient of  $V_{EB}$  itself depends on the temperature, creating a small error in constant reference generation.

From the simulations, the CTAT (Complementary to Absolute Temperature) voltage at 233 K is:

$$\frac{\partial V_{EB1}}{\partial T} \simeq -1.72 \,\frac{\mathrm{mV}}{\mathrm{K}},\tag{1.18}$$

which is a very similar value to the one obtained from theory.

#### **Positive TC voltage**

From eq. (1.7)

$$V_{EB} = V_T \cdot \ln\left(\frac{I_C}{I_S}\right). \tag{1.19}$$

Using eq. (1.19),  $\Delta V_{EB}$  can be found as

$$\Delta V_{EB} = V_{EB1} - V_{EB2} =$$

(1.20)

$$= V_T \cdot \ln \frac{I_{E1}}{I_{S1}} - V_T \cdot \ln \frac{I_{E2}}{I_{S2}} =$$

(1.21)

$$= V_T \cdot \ln\left(\frac{I_{E1} \cdot I_{S2}}{I_{E2} \cdot I_{S1}}\right). \tag{1.22}$$

Since all the BJT fingers of Q1 and Q2 have the same dimensions, the current saturation of these are equal ( $I_{S1} = I_{S2}$ ). Moreover, their collector currents are:

- $I_{E1} = I_1$ , because Q1 has only 1 finger.

- $I_{E2} = \frac{I_2}{N} = \frac{I_1}{8}$ , since Q2 is composed of 8 fingers (N is the number of fingers).

From these assertions, the derivative of  $\Delta V_{EB}$  can be easily found:

$$\Delta V_{EB} = V_T \cdot \ln(\mathbf{N}) = V_T \cdot \ln(\mathbf{8}), \qquad (1.23)$$

$$\frac{\partial \Delta V_{EB}}{\partial T} = \frac{k}{q} \cdot \ln(8) \simeq 0.179 \,\frac{\text{mV}}{\text{K}} \tag{1.24}$$

which is the required PTAT (Proportional to Absolute Temperature) coefficient.

#### Voltage reference

The numerical values found in the eq. (1.18) and (1.24) can be used in the eq. (1.5):

$$\frac{\partial V_{ref}}{\partial T} = -1.72 \,\frac{\text{mV}}{\text{K}} + 0.179 \,\frac{\text{mV}}{\text{K}} \cdot \frac{R_1}{R_2} = 0, \qquad (1.25)$$

and hence

$$\frac{R_1}{R_2} = \frac{1.72}{0.179} = 9.6. \tag{1.26}$$

In Section 1.1.4 the solution adopted to select the resistors is carefully explained.

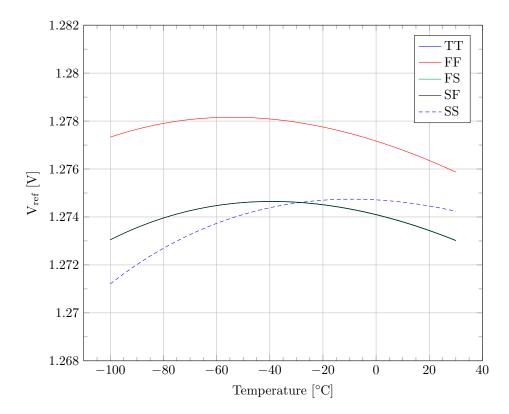

Figure 1.3: bandgap voltage reference  $V_{ref}$  corner values. Results for corners TT, FS, and SF cannot be distinguished since they are perfectly superimposed.

In figure fig. 1.3 the bandgap voltage reference as a function of temperature, provided by schematic simulations, is shown. Since the expected operating temperature is -40 °C, simulations have been done by varying the temperature in a range of  $\pm 60$  °C with respect to -40 °C. In table 1.1 the results of a 1000 step Monte Carlo simulation are reported. The bandgap voltage is more affected by mismatch than process parameters, however, the standard deviation of the  $V_{ref}$  is still low (6.86 mV). In fact, the maximum variation of the output  $\Delta V_{ref}$  is 40 mV. This value satisfies the requirements of the project.

|          | TEMP. [°C] | Min [V]        | Max [V]        | μ [V]          | $\sigma [{\rm mV}]$ |

|----------|------------|----------------|----------------|----------------|---------------------|

| Process  | -40<br>27  | 1.269<br>1.265 | 1.282<br>1.282 | 1.275<br>1.273 | 2.04<br>2.53        |

|          | -40        | 1.255          | 1.296          | 1.275          | 6.85                |

| Mismatch | 27         | 1.255          | 1.292          | 1.273          | 6.47                |

Table 1.1: Bandgap process and mismatch Monte Carlo simulations.

Figure 1.4: Start-up circuit for the Bandgap Voltage Reference.

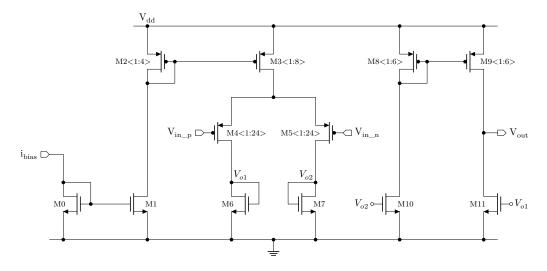

Figure 1.5: Operational amplifier schematic.

#### Start-up circuit

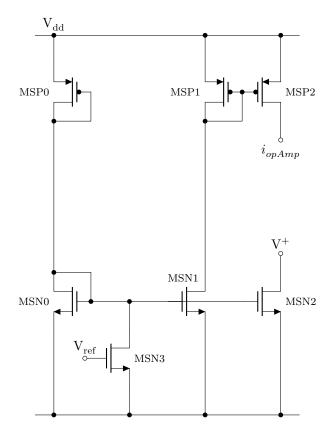

When the circuit is not powered, all transistors carry zero current because they are in the off-state. In some circuits, it may happen that, when the supply is turned on, they remain in the off-state due to the existence of degenerate bias points. In fact, if  $I_1 = I_2 = 0$  A,  $V_{ref} = V^- = 0$  V. Furthermore, if  $V_{SG14} < |V_{tp14}|$  the operational amplifier is not correctly biased. This issue, known as "start-up" problem, is usually solved by adding a mechanism that drives the circuit out of the degenerate bias point when the supply is turned on [1]. The start-up circuit design for this bandgap is shown in fig. 1.4. This is a simple example, where the diode-connected device MSP0 provides a current which flows in the current mirror comprised of MSN0, MSN1 and MSN2 transistors. The MSN0 gate is connected to the gate of MSN1 and MSN2 mirroring the current in these branches. The drain of MSN2 is connected at node  $V^+$  in the bandgap. The current starts to flow in the right branch of the bandgap ( $I_2$ ), raising voltage  $V^+$ , and consequently  $V^-$  (due to the negative feedback loop configuration of the operational amplifier). Therefore, the current starts to flow in the left branch, too  $(I_1)$ , raising the voltage  $V_{ref}$ . This is possible only if the operational amplifier is correctly biased. To solve this problem, the current mirror in the start-up circuit composed of transistor MSP1 and MSP2 provides the current needed by the operational amplifier to work correctly. When  $V_{ref}$  is high enough, MSN3 turns on, connecting the gates of MSN0, MSN1 and MSN2 to ground and turning off these transistors, and consequently, the entire start-up circuit. The problem of start-up, is that it generally requires careful analysis and simulation. The supply voltage must be ramped from zero in a dc sweep simulation (so that parasitic capacitances do not cause false start-up) as well as in a transient simulation and the behavior of the circuit examined for each supply voltage.

#### 1.1.2 Operational Amplifier

The schematic of the operational amplifier used in the bandgap described in the previous subsection is shown in fig. 1.5. The bias current is provided from pin  $I_{bias}$ , and is mirrored in the first stage of the amplifier through M0, M1, M2 and M3 transistors.

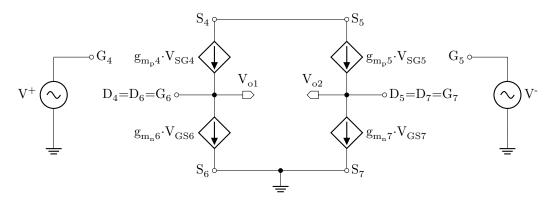

Figure 1.6: Small signal model of the first stage of the operational amplifier.

#### **Small signal Model**

In the first stage (M3-M4-M5-M6-M7) of the operational amplifier, M3, for the small signal model, is a current generator (as it is operated in a current mirror configuration), so it is considered like an open circuit. M4 and M5 have the same dimension and the same bias current, the same goes for M6 and M7. So  $g_{m_p4} = g_{m_p5} = g_{m_p1}$  and  $g_{m_n6} = g_{m_n7} = g_{m_n}$ . The equivalent small signal model of the first stage is shown in fig. 1.6. The Kirchoff current Law is applied to node  $S_4$ , obtaining:

$$g_{m_p1} \cdot V_{SG4} = -g_{m_p1} \cdot V_{SG5} \tag{1.27}$$

$$V_{S4} - V^+ = -(V_{S4} - V^-)$$

(1.28)

$$V_{S4} = \frac{V^+ + V^-}{2}.$$

(1.29)

With the help of eq. (1.29), the current balance in  $V_{o1}$  is:

$$g_{m_p1} \cdot V_{SG4} = g_{m_n} \cdot V_{GS6} \tag{1.30}$$

$$g_{m_p1} \cdot (V_{S4} - V^+) = g_{m_n} \cdot V_{o1} \tag{1.31}$$

$$V_{o1} = \frac{g_{m_p1}}{g_{m_n}} \frac{V^- - V^+}{2},$$

(1.32)

and similarly  $V_{o2}$ :

$$V_{o2} = \frac{g_{m_p1}}{g_{m_n}} \frac{V^+ - V^-}{2}.$$

(1.33)

Using equations (1.32) and (1.33) it is possible to find:

$$V_{o2} - V_{o1} = \frac{g_{m_p 1}}{g_{m_n}} \left( V^+ - V^- \right).$$

(1.34)

The second stage of the operational amplifier is composed of MOS M8, M9, M10 and M11. M10 and M11 have the same dimensions and bias currents of MOS M6 and M7 of the first stage. So,  $g_{m_n10} = g_{m_n11} = g_{m_n}$ . M8 and M9 are equal, too, obtaining  $g_{m_p8} = g_{m_p9} = g_{m_p2}$ .  $r_{DS9}$  and  $r_{DS11}$  are in parallel configuration, so  $r_{DS} = r_{DS9} / r_{DS11}$ . Applying Kirchoff

Figure 1.7: Small signal model of the second stage of the operational amplifier.

current law to node  $G_8$ :

$$g_{m_p2} \cdot V_{SG8} = g_{m_n} \cdot V_{GS10} \tag{1.35}$$

$$V_{g8} = -\frac{g_{m_n}}{g_{m_p2}} V_{o2}.$$

(1.36)

The current balance in *V*<sub>out</sub>:

$$g_{m_p2} \cdot V_{SG9} + \frac{0 - V_{out}}{r_{DS}} = g_{m_n} \cdot V_{GS11}$$

(1.37)

$$V_{out} = -r_{DS} \cdot \left( g_{m_p 2} V_{g8} + g_{m_n} V_{o1} \right).$$

(1.38)

With the help of eq. (1.36):

$$V_{out} = r_{DS} \cdot g_{m_n} \left( V_{o2} - V_{o1} \right), \tag{1.39}$$

and finally, using eq. (1.34)

$$V_{out} = r_{DS} \cdot g_{m_0 1} \left( V^+ - V^- \right). \tag{1.40}$$

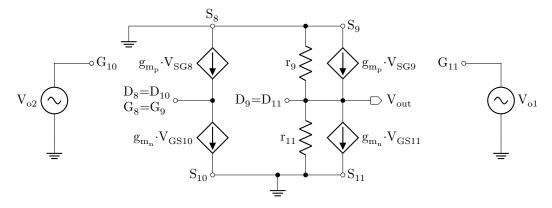

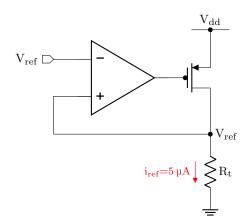

#### 1.1.3 Current Reference

The 5  $\mu$ A current reference,  $I_{ref}$ , is generated by means of the circuit shown in fig. 1.8. In order to obtain a constant current, the voltage reference  $V_{ref}$  must be independent of temperature, process parameters and supply voltage variations. The Bandgap Voltage Reference, described in section 1.1.1 has been designed to accomplish this task. With a fixed  $V_{ref}$ , it is possible to select  $R_t$  in order to have:

$$I_{ref} = \frac{V_{ref}}{R_t} = 5\,\mu\text{A} \tag{1.41}$$

For  $R_t$  to be temperature independent, two different types of resistors have to be used:

- $R_p$ , whose value is directly proportional to the temperature

- $R_n$ , whose value is inversely proportional to the temperature.

Figure 1.8: Semplified schematic of the current generator design for GAPS Front-end.

The sum of these two resistors must be constant as a function of temperature:

$$R_t = R_p(T) + R_n(T).$$

(1.42)

Two resistors,  $R_p$  and  $R_n$ , have been selected using the method explained in section 1.1.4 in order to obtain a fixed  $I_{ref} = 5 \,\mu\text{A}$ . The complete schematic of the current generator is shown in fig. 1.9.

The current  $I_{ref}$  has to be mirrored in another branch of the circuit in order to be used to generate the other currents needed by the GAPS front-end. OP2, in buffer configuration, is used to mirror the voltage  $V_{ref}$  in the right branch of the circuit. Since the PMOS M12 and M13 have the same gate, drain and source voltages, the current  $I_{mir}$  is close to equal to the current  $I_{ref}$ . This has been verified by simulation, in temperature domain, and can be seen in fig. 1.10.

In order to guarantee the asymptotic stability and evaluate the robustness of the system, of the two negative feedback of OP1 and OP2, the phase margin has been extracted from simulations. The results are show in table 1.2.

|     | TEMP. [°C] | TT [°]         | FF [°] | FS [°]         | SF [°] | SS [°]         |

|-----|------------|----------------|--------|----------------|--------|----------------|

| 0P1 | -40<br>27  | 67.77<br>62.38 |        | 72.81<br>66.09 |        |                |

| 0P2 | -40<br>27  | 55.84<br>59.41 |        | 57.08<br>61.71 |        | 58.01<br>62.63 |

Table 1.2: phase margin of OP1 and OP2 feedback loop.

Afterwards, the current  $I_{mir}$  has been evaluated by varying: temperature, supply voltage and process parameters. Moreover a 1000 step mismatch and process simulation have been done. The results are shown in tables (1.3) and (1.4). The most critical cases are the FF and SS corners and the process Monte Carlo simulations.

Figure 1.10: values of current  $I_{mir}$  with respect to  $I_{ref}$ .

| V <sub>dd</sub> [V] | TEMP. [°C] | TT [μA] | FF [µA] | FS [µA] | SF [µA] | SS [µA] |

|---------------------|------------|---------|---------|---------|---------|---------|

|                     | -100       | 4.985   | 5.725   | 4.980   | 4.987   | 4.415   |

| 1 ( )               | -40        | 5.006   | 5.753   | 5.005   | 5.007   | 4.436   |

| 1.62                | 0          | 5.000   | 5.748   | 4.995   | 4.998   | 4.429   |

|                     | 27         | 4.980   | 5.734   | 4.980   | 4.982   | 4.41    |

|                     | -100       | 4.989   | 5.729   | 4.989   | 4.989   | 4.422   |

| 1.8                 | -40        | 5.012   | 5.761   | 5.012   | 5.012   | 4.447   |

| 1.0                 | 0          | 5.004   | 5.757   | 5.004   | 5.004   | 4.432   |

|                     | 27         | 4.99    | 5.744   | 4.989   | 4.989   | 4.420   |

|                     | -100       | 4.990   | 5.731   | 4.990   | 4.990   | 4.423   |

| 1 09                | -40        | 5.012   | 5.762   | 5.012   | 5.013   | 4.441   |

| 1.98                | 0          | 5.004   | 5.758   | 5.004   | 5.004   | 4.432   |

|                     | 27         | 4.990   | 5.745   | 4.990   | 4.990   | 4.418   |

Table 1.3: Values of current  $I_{mir}$  by varying: supply voltage, temperature and process parameters.

|          | TEMP. [°C] | Min [µA] | Max [µA] | μ [μΑ] | $\sigma$ [nA] |

|----------|------------|----------|----------|--------|---------------|

|          | -100       | 4.340    | 5.697    | 4.990  | 210           |

| cese     | -40        | 4.346    | 5.737    | 5.013  | 215           |

| Process  | 0          | 4.331    | 5.737    | 5.005  | 217           |

| щ        | 27         | 4.312    | 5.726    | 4.991  | 218           |

| ų        | -100       | 4.883    | 5.098    | 4.988  | 34            |

| lato     | -40        | 4.912    | 5.110    | 5.011  | 31            |

| Mismatch | 0          | 4.907    | 5.096    | 5.004  | 30            |

| Μ        | 27         | 4.894    | 5.077    | 4.989  | 29            |

Table 1.4: Process and mismatch Monte Carlo simulations.

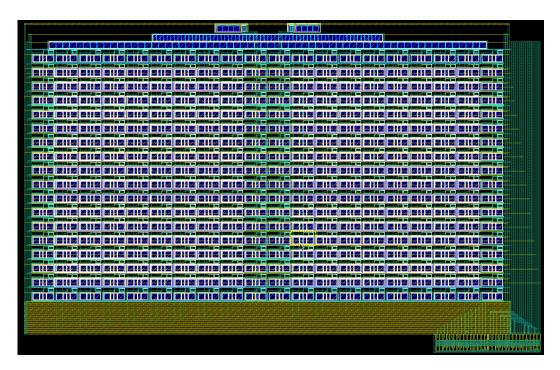

The current reference layout is shown in fig. 1.11. Its dimensions are 460  $\mu$ m×125  $\mu$ m.

#### 1.1.4 Resistors choice

The resistance of an integrated resistor changes with the temperature, mainly due to the variation of charge carriers mobility in conductors, and concentration in semiconductors. In each CMOS technology, resistors can be made with different materials. In a material where the resistance increases with an increase in temperature, the material is said to have a positive temperature coefficient. When resistance decreases with an increase in temperature, the material is said to have a negative temperature coefficient. The resistance also depends on the applied voltage and the model adopted. In the 180 nm CMOS technology,

Figure 1.11: current reference layout.

the resistance model used for the GAPS project is the following [8]:

$$R(T,V) = R_0 \cdot \left(1 + T_{C1} \cdot \Delta T + T_{C2} \cdot \Delta T^2\right) \cdot \left(1 + V_{C1} \cdot \Delta V + V_{C2} \cdot \Delta V^2\right),$$

(1.43)

where  $\Delta T = T - T_0$  (expressed in K),  $\Delta V$  is the voltage drop across the resistor,  $T_{C1}$  [K<sup>-1</sup>] and  $T_{C2}$ [K<sup>-2</sup>] are temperature coefficients of the resistor while  $V_{C1}$ [V<sup>-1</sup>] and  $V_{C2}$ [V<sup>-2</sup>] are voltage coefficients of the resistor.  $R_0$  is the resistance value at  $T_0 = 25$  °C and 0 V applied, which is related to sheet resistance,  $R_{sh}$ , by the following equation [9]:

$$R_0 = R_{sh} \cdot \frac{L}{W},\tag{1.44}$$

where W and L are the layout drawn width and length. If  $\Delta V$  is constant, like in the circuit shown in fig. 1.8, eq. (1.43) can be rewritten as:

$$R(T) = k_R \cdot \frac{L}{W} \cdot \left(1 + T_{C1} \cdot \Delta T + T_{C2} \cdot \Delta T^2\right).$$

(1.45)

where  $k_R = R_{sh} \cdot k_V$  and  $k_V = (1 + V_{C1} \cdot \Delta V + V_{C2} \cdot \Delta V^2)$ .

After selecting two resistance technologies, *a* and *b*, the resistance  $R_t$  (eq. (1.42)) can be rewritten as:

$$R_t(T) = R_p(T) + R_n(T) =$$

(1.46)

$$= k_{p} \cdot \frac{L_{p}}{W_{p}} \cdot \left(1 + T_{C1,p} \cdot \Delta T + T_{C2,p} \cdot \Delta T^{2}\right) + k_{n} \cdot \frac{L_{n}}{W_{n}} \cdot \left(1 + T_{C1,n} \cdot \Delta T + T_{C2,n} \cdot \Delta T^{2}\right)$$

(1.47)

where  $R_p$  is the *a* technology resistor and  $R_n$  is the *b* technology resistor.

At first, the values  $x_p = \frac{L_p}{W_p}$  and  $x_n = \frac{L_n}{W_n}$  that minimize  $R_t(T) - R_p(T) - R_n(T)$ , for some temperatures  $[T_{min}, T_{min} + T_s, \dots, T_{max} - T_s, T_{max}]$ , have to be found ( $T_s$  is the selected temperature step). This problem can be expressed in the form  $\underline{y} = X \cdot \underline{\theta} + \underline{\epsilon}$ , where  $\underline{y} = \underline{R_t}$  and  $\underline{\theta} = [x_p, x_n]$ , namely:

$$\begin{bmatrix} R_t \\ \dots \\ R_t \end{bmatrix} = \begin{bmatrix} k_p \cdot \left(1 + T_{C1,p} \cdot \Delta T_{min} + T_{C2,p} \cdot \Delta T_{min}^2\right) & k_n \cdot \left(1 + T_{C1,n} \cdot \Delta T_{min} + T_{C2,n} \cdot \Delta T_{min}^2\right) \\ \dots \\ k_p \cdot \left(1 + T_{C1,p} \cdot \Delta T_{max} + T_{C2,p} \cdot \Delta T_{max}^2\right) & k_n \cdot \left(1 + T_{C1,n} \cdot \Delta T_{max} + T_{C2,n} \cdot \Delta T_{max}^2\right) \end{bmatrix} \begin{bmatrix} x_p \\ x_n \end{bmatrix}$$

(1.48)

Using the method of least squares

$$\underline{\hat{\theta}} = \left(X^T \cdot X\right)^{-1} \cdot X^T \cdot \underline{y},\tag{1.49}$$

the error for each selected temperature T is

$$\underline{\varepsilon_T} = \underline{R_t} - \underline{X_{T,p}} \cdot x_p - \underline{X_{T,n}} \cdot x_n, \qquad (1.50)$$

where:

$$\frac{X_{T,p}}{M} = \begin{bmatrix} k_p \cdot (1 + T_{C1,p} \cdot \Delta T_{min} + T_{C2,p} \cdot \Delta T_{min}^2) \\ \dots \\ k_p \cdot (1 + T_{C1,p} \cdot \Delta T_{max} + T_{C2,p} \cdot \Delta T_{max}^2) \end{bmatrix}$$

(1.51)

and

$$\underline{X_{T,n}} = \begin{bmatrix} k_n \cdot (1 + T_{C1,n} \cdot \Delta T_{min} + T_{C2,n} \cdot \Delta T_{min}^2) \\ \dots \\ k_p \cdot (1 + T_{C1,n} \cdot \Delta T_{max} + T_{C2,n} \cdot \Delta T_{max}^2) \end{bmatrix}.$$

(1.52)

The Root-Mean-Square Error (RMSE), for the couple of resistance technologies (a, b), can be calculated:

$$RMSE_{a,b} = \sqrt{\frac{\sum_{n=T_{min}}^{T_{max}} \varepsilon_n^2}{\frac{T_{max} - T_{min}}{T_s}}}.$$

(1.53)

The main goal is to find two resistor technologies that minimize the RMSE. This task has been performed with two *for* cycles:

where Ntec\_pos is the number of resistor technologies with positive temperature coefficient while Ntec\_neg is the number of resistor technologies with negative temperature coefficient. Given all RMSE values, two technologies ( $tec_1, tec_2$ ) can be selected such that  $RMSE_{tec_1, tec_2}$  is minimum and  $x_{p,(tec_1, tec_2)} \ge 0, x_{n,(tec_1, tec_2)} \ge 0$ .

Using this method, the two types of resistor chosen are: N+ Diffusion resistor without silicide (positive temperature coefficient) and P+ Poly resistor without silicide (negative temperature coefficient).

#### 1.1.5 3-bit Digital to Analog Converter

As can be seen in tables 1.3 and 1.4, the mimimum and the maximum value of the current  $I_{mir}$  are respectively 4.31 µA (in process simulations at 27 °C) and 5.76 µA (in corners simulations, case FF at -40 °C with 1.98 V supply voltage). A DAC has been designed in order to compensate for this variation and obtain a current as close as possible to the required 5 µA. For dimension restrictions, design simplicity and correction effectiveness a 3-bit DAC, in binary weighted configuration, has been chosen [10]. Having 3 bits available, the DAC lsb ( $I_{LSB}$ ) was initially obtained by calculating:

$$I_{LSB} = \frac{I_{max} - I_{min}}{2^3 - 1} \tag{1.54}$$

With an error margin  $\Delta i$  for both  $I_{min}$  and  $I_{max}$ , it can be obtained:

$$I_{LSB} = \frac{(I_{max} + \Delta i) - (I_{min} - \Delta i)}{2^3 - 1} = \frac{I_{max} - I_{min} + 2\Delta i}{2^3 - 1}$$

(1.55)

By placing  $\Delta i = 0.3 \,\mu$ A:

$$I_{LSB} \approx \frac{2\,\mu A}{7} = 285.71\,\mathrm{nA}$$

(1.56)

For layout design accuracy, current mirrors MOS must have the same L and multiple W with respect to the MOS of the main branch of the current mirror. For this reason, MOS with the same W and different number of fingers have been used. The LSB found in eq. (1.56) cannot be precisely obtained, by following the previous tips, due to the fact that MOS W cannot be modified at will. In order to contain the DAC dimensions, the  $I_{LSB}$  is found in this way:

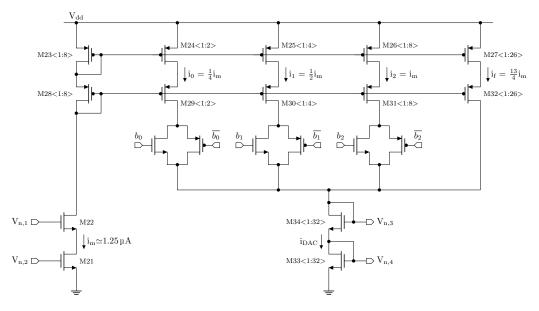

- a first current mirror with a 1:4 ratio with respect to  $I_{mir}$  (generated by the current generator described in section 1.1.3) permits to obtain a 1.25 µA current ( $I_m$ );

- a second current mirror with a 1:4 ratio with respect to  $I_m$  permits to obtain a 312.5 nA current ( $I_{LSB}$ ).

The 3 currents obtained with these 3 bit are:

- bit 0: 312.5 nA (ratio 1:4)

- bit 1: 625 nA (ratio 1:2)

- bit 2: 1.25 µA (ratio 1:1)

The schematic of the 3-bit DAC is shown in fig. 1.12. The final current  $I_{DAC}$  is calculated in this way:

$$I_{DAC} = b_0 \cdot \frac{1}{4} I_m + b_1 \cdot \frac{1}{2} I_m + b_2 \cdot I_m + I_f$$

(1.57)

The number of fingers of the rightmost branch has been chosen in a way that allows to have  $I_{DAC} = 5 \,\mu\text{A}$  with 011 bit combination. In fact:

$$I_{DAC,011} = \frac{1}{4}I_m + \frac{1}{2}I_m + \frac{13}{4}I_m = 4I_m = 5\,\mu\text{A}$$

(1.58)

As described in section 1.1.3, the current generator is affected by process variations because of the resistor  $R_t$ . Its corner values may vary from  $R_t - 15\%$  to  $R_t + 15\%$ . The 3-bit DAC just described can easily correct these cases. For example, if  $R_t$  value is 15% greater than its nominal value, a 1.1 µA  $I_m$  and a 275 nA  $I_{LSB}$  are obtained. Following the eq. (1.57) and with a 101 DAC combination, the new current  $I_{DAC}$  can be calculated as:

$$I_{DAC,101} = \frac{1}{4}I_m + I_m + \frac{13}{4}I_m = \frac{9}{2}I_m = 4.95\,\mu\text{A}$$

(1.59)

The value just found is very close to the required 5  $\mu$ A. The  $R_t$  – 15 % case is similarly corrected with the 001 DAC combination.

The previous assumptions have been verified by simulations, as shown in table 1.5.

The entire current reference and 3-bit DAC layout is shown in fig. 1.13. Its dimensions are  $460 \,\mu m \times 300 \,\mu m$ .

Figure 1.12: 3-bit DAC schematic.

Figure 1.13: current reference and 3-bit DAC layout.

| Bias [bit] | TEMP. [°C] | TT [μA] | FF [µA] | FS [μA] | SF [μA] | SS [µA] |

|------------|------------|---------|---------|---------|---------|---------|

|            | -100       | 4.052   | 4.654   | 4.052   | 4.053   | 3.590   |

| 000        | -40        | 4.072   | 4.681   | 4.072   | 4.072   | 3.608   |

| 000        | 0          | 4.066   | 4.678   | 4.066   | 4.066   | 3.601   |

|            | 27         | 4.054   | 4.667   | 4.054   | 4.054   | 3.589   |

|            | -100       | 4.364   | 5.012   | 4.364   | 4.364   | 3.866   |

| 001        | -40        | 4.385   | 5.041   | 4.385   | 4.385   | 3.885   |

| 001        | 0          | 4.379   | 5.038   | 4.379   | 4.379   | 3.878   |

|            | 27         | 4.365   | 5.026   | 4.365   | 4.366   | 3.865   |

|            | -100       | 4.676   | 5.37    | 4.675   | 4.676   | 4.142   |

| 010        | -40        | 4.698   | 5.401   | 4.698   | 4.698   | 4.163   |

| 010        | 0          | 4.691   | 5.398   | 4.691   | 4.691   | 4.155   |

|            | 27         | 4.677   | 5.385   | 4.677   | 4.677   | 4.141   |

|            | -100       | 4.987   | 5.728   | 4.987   | 4.988   | 4.418   |

| 011        | -40        | 5.011   | 5.761   | 5.011   | 5.012   | 4.44    |

| 011        | 0          | 5.004   | 5.758   | 5.004   | 5.004   | 4.432   |

|            | 27         | 4.989   | 5.744   | 4.989   | 4.989   | 4.417   |

|            | -100       | 5.299   | 6.086   | 5.299   | 5.299   | 4.694   |

| 100        | -40        | 5.325   | 6.121   | 5.325   | 5.325   | 4.718   |

| 100        | 0          | 5.317   | 6.117   | 5.317   | 5.317   | 4.709   |

|            | 27         | 5.301   | 6.103   | 5.301   | 5.301   | 4.694   |

|            | -100       | 5.611   | 6.444   | 5.611   | 5.611   | 4.97    |

| 101        | -40        | 5.638   | 6.481   | 5.638   | 5.638   | 4.995   |

| 101        | 0          | 5.63    | 6.477   | 5.630   | 5.630   | 4.986   |

|            | 27         | 5.613   | 6.462   | 5.613   | 5.613   | 4.97    |

|            | -100       | 5.923   | 6.802   | 5.922   | 5.923   | 5.246   |

| 110        | -40        | 5.951   | 6.841   | 5.951   | 5.951   | 5.273   |

| 110        | 0          | 5.942   | 6.837   | 5.942   | 5.942   | 5.263   |

|            | 27         | 5.925   | 6.82    | 5.925   | 5.925   | 5.246   |

|            | -100       | 6.234   | 7.160   | 6.234   | 6.234   | 5.523   |

| 111        | -40        | 6.264   | 7.201   | 6.264   | 6.264   | 5.550   |

| 111        | 0          | 6.255   | 7.197   | 6.255   | 6.255   | 5.540   |

|            | 27         | 6.236   | 7.179   | 6.236   | 6.236   | 5.522   |

Table 1.5: Values of current  $I_{DAC}$  by varying: DAC combinations, temperature and process parameters.

#### 1.1.6 Current mirrors

Each block, described in appendix B, needs a specific current to work properly; these values are listed in table 1.6. All the required currents are a multiple of  $5 \,\mu\text{A}$  (except the Shaper\_2 block), so they can be easily obtained using a current generator and current mirrors, each with a different gain [8]. The Shaper\_2 block current is generated using an 8-finger MOS in the main branch of the current mirrors and a 3-finger MOS in the mirror branch, obtaining a gain factor of  $\frac{3}{8}$  (all the fingers must be characterized by the same W and L).

| IP BLOCK       | NOMINAL | MIRROR GAIN          |

|----------------|---------|----------------------|

| CSA_1          | 10 µA   | $\times 2$           |

| CSA_2          | 50 µA   | $\times 10$          |

| CSA_3          | 250 μΑ  | $\times 50$          |

| INTEGRATOR     | 20 µA   | $\times 4$           |

| THRESHOLD      | 15 µA   | ×3                   |

| SHAPER_1       | 25 μΑ   | $\times 5$           |

| SHAPER_2       | 1.5 µA  | $\times \frac{3}{8}$ |

| DIFFERENTIATOR | 20 µA   | ×4                   |

| COMPARATOR     | 50 µA   | $\times 10$          |

| S&H            | 10 µA   | ×2                   |

Table 1.6: Currents needed by GAPS Front-end IP blocks

Lastly, the generated current  $I_{DAC}$  is mirrored in other branches with a mirror gain dependent on the block to bias. The required mirror gains are already listed in table 1.6. All the current mirrors are designed in cascode configuration in order to decrease the effects of process and mismatch parameters. As first analysis, the current mirrors, without considering the layout parasitic resistances and capacitances, have been evaluated for temperature range from -100 °C to 30 °C and for all the process cases. Results are shown in table 1.7. All these values are obtained using the current generator previously described. In order to obtain a current as similar as possible to the required one, in TT, FS, and SF cases the 3-bit DAC has been set to 011, in FF case it has been set to 001 and, finally, the SS case has been corrected with the 101 DAC code. The maximum relative errors of the simulation with respect to the ideal values, for each block, are:

- CSA\_1: FF case, -40 °C, absolute error of 0.25  $\mu$ A and a relative error of 2.5 %.

- CSA\_2: FF case, –40 °C and 0 °C, absolute error of 0.40  $\mu A$  and a relative error of 0.8 %.

- CSA\_3: SS case, -100 °C, absolute error of 7.07  $\mu$ A and a relative error of 2.82 %.

- Integrator: FF case, -40 °C, absolute error of 0.7  $\mu$ A and a relative error of 3.5 %.

- Threshold Generator: FF case,  $-40\,^\circ\text{C},$  absolute error of 0.47  $\mu\text{A}$  and a relative error of 3.13 %.

- 1 Design of IP blocks in a 180 nm CMOS technology

- Shaper\_1: SS case, -100 °C, absolute error of 0.67 μA and a relative error of 2.68 %.

- Shaper\_2: SS case, -100 °C, absolute error of 0.02  $\mu$ A and a relative error of 1.33 %.

- Differentiator: SS case,  $-100\,^\circ\text{C},$  absolute error of  $0.53\,\mu\text{A}$  and a relative error of 2.65 %.

- Comparator: SS case, -100 °C, absolute error of 1.37  $\mu$ A and a relative error of 2.74 %.

- S&H: SS case, -100 °C, absolute error of 0.25  $\mu$ A and a relative error of 2.5 %.

The maximum relative error is found for the Integrator. SS case at -100 °C is, in general, the worst case scenario for the mirrored currents.

As a second analysis, a mismatch simulation for the typical case, at -40 °C and 3-bit DAC code set to 011, has been carried out. The results are listed in table 1.8, has been carried out. The mean results are in line with the required ones. The maximum and minimum values can be easily corrected by modifying the 3-bit DAC code, as demonstrated for the process simulations shown in table 1.7.

As third analysis, simulations considering the layout parasitic resistances and capacitances have been run. Simulations setting are always: typical case, at -40 °C and 3-bit DAC code set to 011. Results are shown in table 1.9.

| Analog block | TEMP. [°C] | TT [μA] | FF [µA] | FS [µA] | SF [µA] | SS [µA] | id. [µA] |

|--------------|------------|---------|---------|---------|---------|---------|----------|

| 1            | -100       | 10.12   | 10.20   | 10.11   | 10.14   | 10.04   |          |

|              | -40        | 10.19   | 10.25   | 10.19   | 10.19   | 10.15   | 10       |

| CSA_         | 0          | 10.16   | 10.23   | 10.16   | 10.16   | 10.12   | 10       |

| Ŭ            | 27         | 10.13   | 10.20   | 10.13   | 10.13   | 10.09   |          |

| CSA_2        | -100       | 49.52   | 49.93   | 49.35   | 49.63   | 48.63   | 50       |

|              | -40        | 50.06   | 50.40   | 50.04   | 50.09   | 49.86   |          |

|              | 0          | 50.03   | 50.40   | 50.02   | 50.05   | 49.82   |          |

|              | 27         | 49.90   | 50.29   | 49.88   | 49.91   | 49.67   |          |

|              | -100       | 247.42  | 249.50  | 246.56  | 247.99  | 242.93  |          |

| CSA_3        | -40        | 250.27  | 251.99  | 250.17  | 250.42  | 249.20  | 250      |

| CSF          | 0          | 250.15  | 252.02  | 250.05  | 250.25  | 249.07  | 250      |

| 0            | 27         | 249.46  | 251.44  | 249.39  | 249.54  | 248.34  |          |

| )r           | -100       | 20.46   | 20.61   | 20.42   | 20.48   | 20.30   |          |

| Integrator   | -40        | 20.57   | 20.70   | 20.57   | 20.57   | 20.50   | 00       |

| fegj         | 0          | 20.51   | 20.65   | 20.51   | 20.51   | 20.44   | 20       |

| Int          | 27         | 20.43   | 20.58   | 20.43   | 20.43   | 20.35   |          |

| -i           | -100       | 15.29   | 15.40   | 15.26   | 15.31   | 15.17   | 15       |

| Thr. Gen.    | -40        | 15.38   | 15.47   | 15.37   | 15.38   | 15.33   |          |

| L.           | 0          | 15.34   | 15.44   | 15.36   | 15.34   | 15.28   |          |

| Ē            | 27         | 15.28   | 15.39   | 15.28   | 15.28   | 15.22   |          |

| Shaper_1     | -100       | 24.78   | 24.98   | 24.70   | 24.83   | 24.33   | 25       |

|              | -40        | 25.04   | 25.21   | 25.03   | 25.05   | 24.94   |          |

|              | 0          | 25.02   | 25.20   | 25.01   | 25.03   | 24.92   |          |

|              | 27         | 24.95   | 25.15   | 24.95   | 24.96   | 24.84   |          |

| 5            | -100       | 1.50    | 1.51    | 1.50    | 1.50    | 1.48    |          |

| Shaper_2     | -40        | 1.50    | 1.51    | 1.50    | 1.50    | 1.50    | 1 5      |

| lap          | 0          | 1.50    | 1.51    | 1.50    | 1.50    | 1.50    | 1.5      |

| Sł           | 27         | 1.50    | 1.51    | 1.50    | 1.49    | 1.49    |          |

|              | -100       | 19.83   | 20.00   | 19.76   | 19.87   | 19.47   |          |

| iff.         | -40        | 20.03   | 20.17   | 20.02   | 20.04   | 19.95   | 20       |

| Di           | 0          | 20.02   | 20.16   | 20.01   | 20.02   | 19.93   |          |

|              | 27         | 19.96   | 20.12   | 19.96   | 19.97   | 19.87   |          |

|              | -100       | 49.52   | 49.94   | 49.35   | 49.63   | 48.63   |          |

| .du          | -40        | 50.07   | 50.41   | 50.04   | 49.63   | 49.86   | 50       |

| Comp.        | 0          | 50.04   | 50.41   | 50.02   | 50.10   | 49.83   |          |

|              | 27         | 49.90   | 50.30   | 49.89   | 49.91   | 49.68   |          |

|              | -100       | 9.93    | 10.00   | 9.90    | 9.95    | 9.75    |          |